# EPSON®

EQUITYL

Personal Computer SERVICE MANUAL EPSON AMERICA, INC.

May for your

# EQUITY I+ TECHNICAL MANUAL

Seiko Epson Corporation Nagano, Japan

## FCC COMPLIANCE STATEMENT

This equipment uses and generates radio frequency energy and it not installed and used properly, that is in strict accordance with the manufacture's instructions, may cause interference to radio and television reception.

It has been type tested and found to comply with limits for a Class B computing device in accordance with Sub-part J of Part 15 of FCC Rules, which are designed to provide reasonable protection against such interference in a residential installation. However, there is no guarantee that interference will not occur in a particular installation. If this equipment dose cause interference to radio or television reception, which can be determined by turning the equipment on and off, the user is encouraged to try to correct the interference by one or more of the following measures:

- . reorient the receiving antenna

- . relocate the computer with respect to the receiver

- . move the computer away from the receiver

- . plug the computer into a different outlet so that the computer and receiver are on different branch circuits

If necessary, the user should consult the dealer or an experienced radio/television technician for additional suggestions. The user may find the following booklet, prepared by the Federal Communications Commission, helpful:

"How to Identify and Resolve Radio – TV interference Problems. "This booklet is available from the U.S. Government Printing Office, Washington. D.C., 20402, Stock No. 044 – 000 – 00345 – 4.

You can determine whether your computer is causing interference by turning it off. If the interference stops, it was probably caused by the computer or its peripheral devices. To further isolate the problem, disconnect either the peripheral device or its I/O cable.

These devices usually require shielded cable. For Epson peripheral devices, you can obtain the proper shielded cable from your dealer. For non-Epson devices, contact the manufacturer or dealer for assistance.

#### Seiko Epson Corporation, Nagano, Japan

(c) 1987 by Seiko Epson Corporation All rights reserved.

Printed in Japan

No portion of this document may be reproduced, stored in a retrieval system, or transmitted in any form or by any means, electric, mechanical, photocopying, recording, or otherwise, without the written permission of Epson Corporation. No patent liability is assumed with respect to use of the information contained herein, nor is any liability assumed for damages resulting from use of this text. While every precaution has been taken in the preparation of this book, the publisher assumes no liability for errors or omissions.

Seiko Epson<sup>®</sup> is a registered trademark of Seiko Epson Corporation. Equity  $II + T^{M}$  is trademark of Epson America, Inc. IBM PC<sup>®</sup> is a registered trademark of International Business Machines Corporation.

#### PRECAUTIONS

Precautionary notations throughout the text are categorized relative to 1) personal injury and 2) damage to equipment.

DANGER Signals a precaution which, if ignored, could result in serious or fatal personal injury. Great caution should be exercised in performing procedures preceded by DANGER Headings.

WARNING Signals a precaution which, if ignored, could result in damage to equipment.

The precautionary measures itemized below should always be observed when performing repair/ maintenance procedures.

#### DANGER

- 1. ALWAYS DISCONNECT THE PRODUCT FROM BOTH THE POWER SOURCE AND PERIPHERAL DEVICES PERFORMING ANY MAINTENANCE OR REPAIR PROCEDURE.

- 2. NO WORD SHOULD BE PERFORMED ON THE UNIT BY PERSONS UNFAMILIAR WITH BASIC SAFETY MEASURES AS DICTATED FOR ALL ELECTRONICS TECHNICIANS IN THEIR LINE OF WORK.

- 3. WHEN PERFORMING TESTING AS DICTATED WITHIN THIS MANUAL, DO NOT CONNECT THE UNIT TO A POWER SOURCE UNTIL IN – STRUCTED TO DO SO. WHEN THE POWER SUPPLY CABLE MUST BE CONNECTED, USE EXTREME CAUTION IN WORKING ON POWER SUPPLY AND OTHER ELECTRONIC COMPONENTS.

#### WARNING

- 1. Repairs on Epson product should be performed only by an Epson certified repair technician.

- 2. Make certain that the source voltage is the same as the rated voltage, listed on the serial number/rating plate. If the Epson product has a primary AC rating different from available power source, do not connect it to the power source.

- Always verify that the Epson product has been disconnected from the power source before removing or replacing printed circuit boards and/or individual chips.

- 4. In order to protect sensitive microprocessors and circuitry, use static discharge equipment, such as anti-static wrist straps, when accessing internal components.

- 5. Replace malfunctioning components only with those components by the manufacture; introduction of second source ICs or other non approved components may damage the product and void any applicable Epson warranty.

| REVISION | ISSUE DATE     | REVISION PAGE |

|----------|----------------|---------------|

| REV.A    | September 1987 | -             |

|          | -              |               |

|          |                |               |

|          |                |               |

|          |                |               |

|          |                |               |

|          |                |               |

|          |                |               |

|          |                |               |

|          |                |               |

.

# TABLE OF CONTENTS

- CHAPTER 1. PRODUCT DESCRIPTION ... Describes the features and specifications of the computer, illustrates system components, and lists the logic configuration of the primary circuit board.

- CHAPTER 2. PRINCIPLES OF OPERATION . . . Details the functional organization of the logic circuitry. This chapter also illustrates the gate array pin configurations.

- CHAPTER 3. OPTIONS . . . Describes option card specifications and the operating principles of the options.

- CHAPTER 4. TROUBLESHOOTING ... Provides instructions for isolating computer malfunctions.

- CHAPTER 5. DISASSEMBLY AND ASSEMBLY ... Describes system disassembly for replace ment of malfunctioning subassemblies.

- CHAPTER 6. ADJUSTMENT AND MAINTENANCE ... Lists the necessary adjustments for unit assembly and servicing.

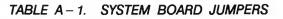

- APPENDIX DIAGRAMS AND REFERENCE MATERIALS... Describes jumper settings and connector pin assignments. This chapter also provides exploded circuit board layout and schematic diagrams for use in conjunction with the text.

Subsequent product modifications will be brought to your attention via Service Bulletins; please revise the text as bulletins are received.

This document is subject to change without notice.

# CABLE OF CONTRACT

이들 사람을 받는 것은 가슴을 알려 가지요? 가지는 것은 가슴이 가슴을 가지고 있었다. 아파 물로 가지 않으시 가려가 가지 않는 것이다. - 4400년 30년 - 1984년 2011년 - 1984년 - 1984년 - 1984년 - 1982년 - 198 - 특별 등 1971년 - 1982년 - 1982년 - 1982년

나는 소설한 것을 받는 것은 가슴을 다니 가지 않는 것을 것을 가지 않는 것을 가지 않는 것이 가지 않다. 것은 것은 것은 것은 것이 있다. 것이 같이 있다. 2014년 - 2017년 2017년 - 2017년

유물 수약 발전된 : 수는 이가 감구로 가지 않는 것이라. 또한 것이라는 것이 가지 않는 것이라. 이가 가지 않는 것 같은 것이라. 이가 있는 것이다. 이가 있는 것이다. 이가 있는 것이다. 이가 가 - 한 2014년 1월 2

PARTER & REAL COLLEGE AND AND COLLEGE AND CONTRACT AND COLLEGE AND COLLEGE

영영 특별과 (1993) 1997년 1 1997년 1998년 1998년 1997년 1997

# **CHAPTER 1**

# **PRODUCT DESCRIPTION**

## TABLE OF CONTENTS

| Section                                 | Title          | Page                    |

|-----------------------------------------|----------------|-------------------------|

| 1.1<br>1.1.1                            | FEATURES       |                         |

| 1.2<br>1.2.1<br>1.2.2<br>1.2.3<br>1.2.4 | SPECIFICATIONS | 1 – 4<br>1 – 6<br>1 – 7 |

## LIST OF FIGURES

| Figure         | Title                         | Page |

|----------------|-------------------------------|------|

| 1 – 1<br>1 – 2 | Main Unit Component Locations |      |

## LIST OF TABLES

| Table | Title                             | Page  |

|-------|-----------------------------------|-------|

| 1 – 1 | ANDRO Board Component Description | 1 – 5 |

요즘 한 눈 집 옷이 아깝다. 유민이 비가가 바라 몰 약

# **1.1 FEATURES**

The Epson EQUITY II + / PC AX2 is a small footprint, high – performance, 80286 – based desktop microcomputer providing complete hardware and software compatibility with the IBM<sup>(R)</sup> PC AT<sup>(R)</sup>.

#### 1.1.1 SYSTEM FEATURES

The system features include:

Two hardware - switchable operating speeds, 8MHz and 10MHz,

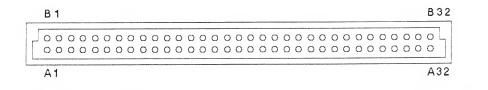

Expansion bus interface for 16-bit and 8-bit expansion boards,

Two jumper-selectable Numeric Processor Extension (NPX) clock speeds,

Independently - selectable wait - state options for system ROM and expansion I/O devices,

BIOS support for a wide range of Hard Disk Drives including those recently supported by the IBM  $PS/2^{(R)}$  line,

Floppy Disk Controller,

Parallel Interface,

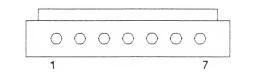

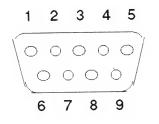

9-pin Asynchronous Serial RS232C Interface,

International Power Supply

1.2MB Floppy Disk Drive

640KB of RAM

The Epson EQUITY II + / PC AX2 Enhanced Model also contains a Hard Disk Controller and a 20MB or 40MB Hard Disk Drive.

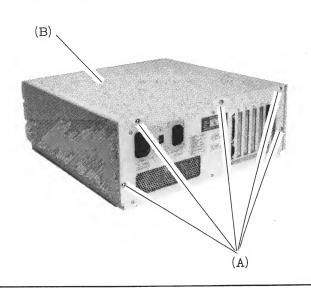

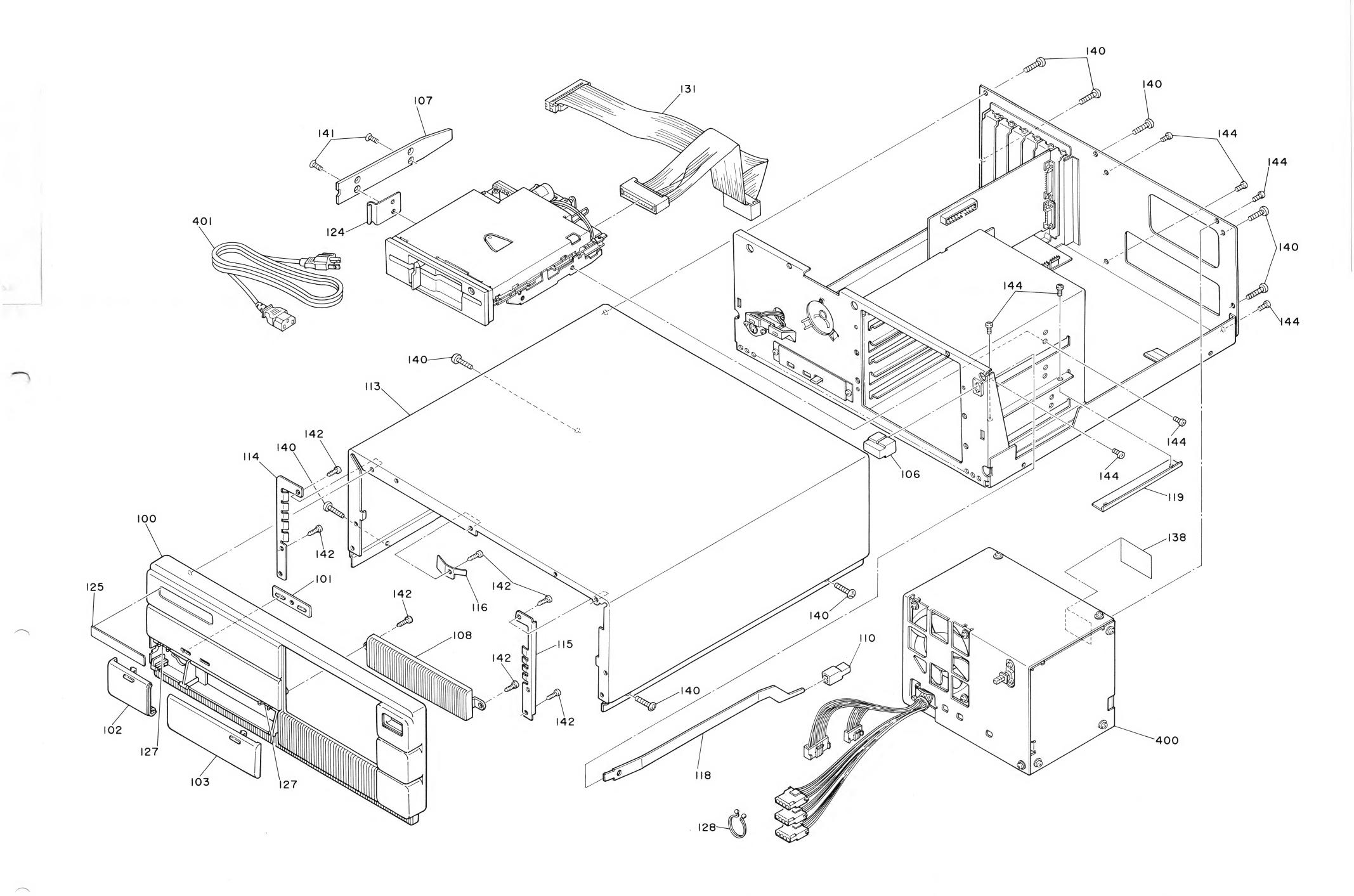

## 1.1.2 HARDWARE CONFIGURATION

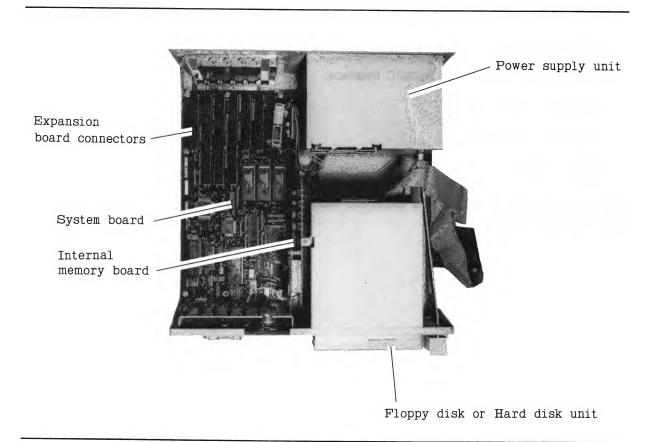

The Epson Equity II + / PC AX2, in its standard configuration, is composed of the main unit and the keyboard. The main unit contains the system board, Epson Multi – Function board (serial, parallel and floppy disk controllers), international power supply, one 1.2MB floppy disk drive, and the expansion board connectors.

In addition to the standard 1.2MB floppy disk drive (FDD) are two floppy disk drive options available: a 720KB 3.5" micro-floppy disk drive, and a 360KB 5.25" mini-floppy disk drive.

There are three optional hard disk drive (HDD) configurations. The factory – installed HDD option provides a Seiko Epson (Model HMD – 720) 20MB half – height HDD with a 69ms average access time. The second HDD option is a Tokico (Model TD5046) 40MB half – height HDD with a 40ms average access time. The third HDD option is a Control Data (Model 94205 – 51) 40MB half – height HDD with an average access time of 28ms.

Video options include a Monochrome Display Adapter, Color Graphics Adapter, Multi – function Graphics Adapter (including Hercules<sup>(TM)</sup> – compatible monochrome graphics, monochrome text and color graphics capabilities), and an EGA – compatible video board.

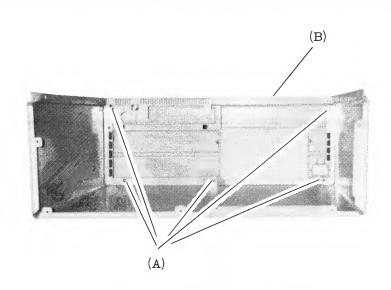

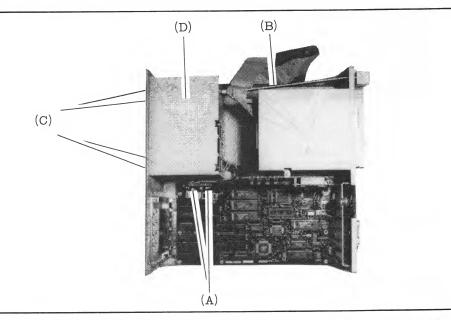

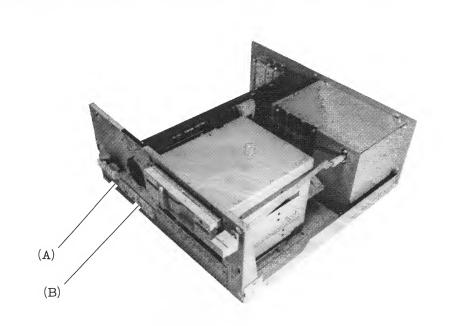

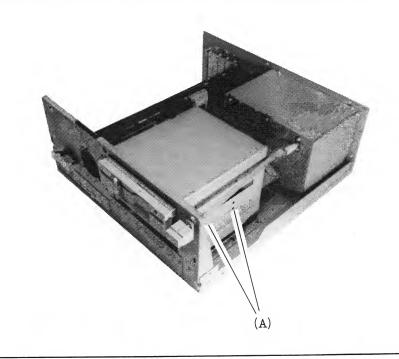

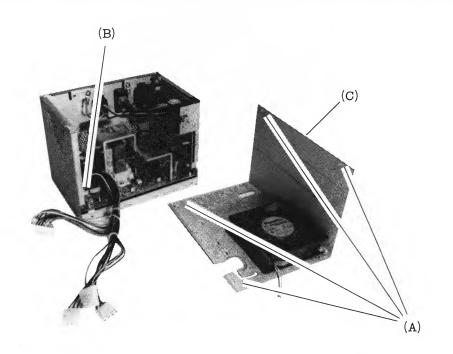

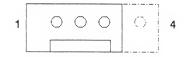

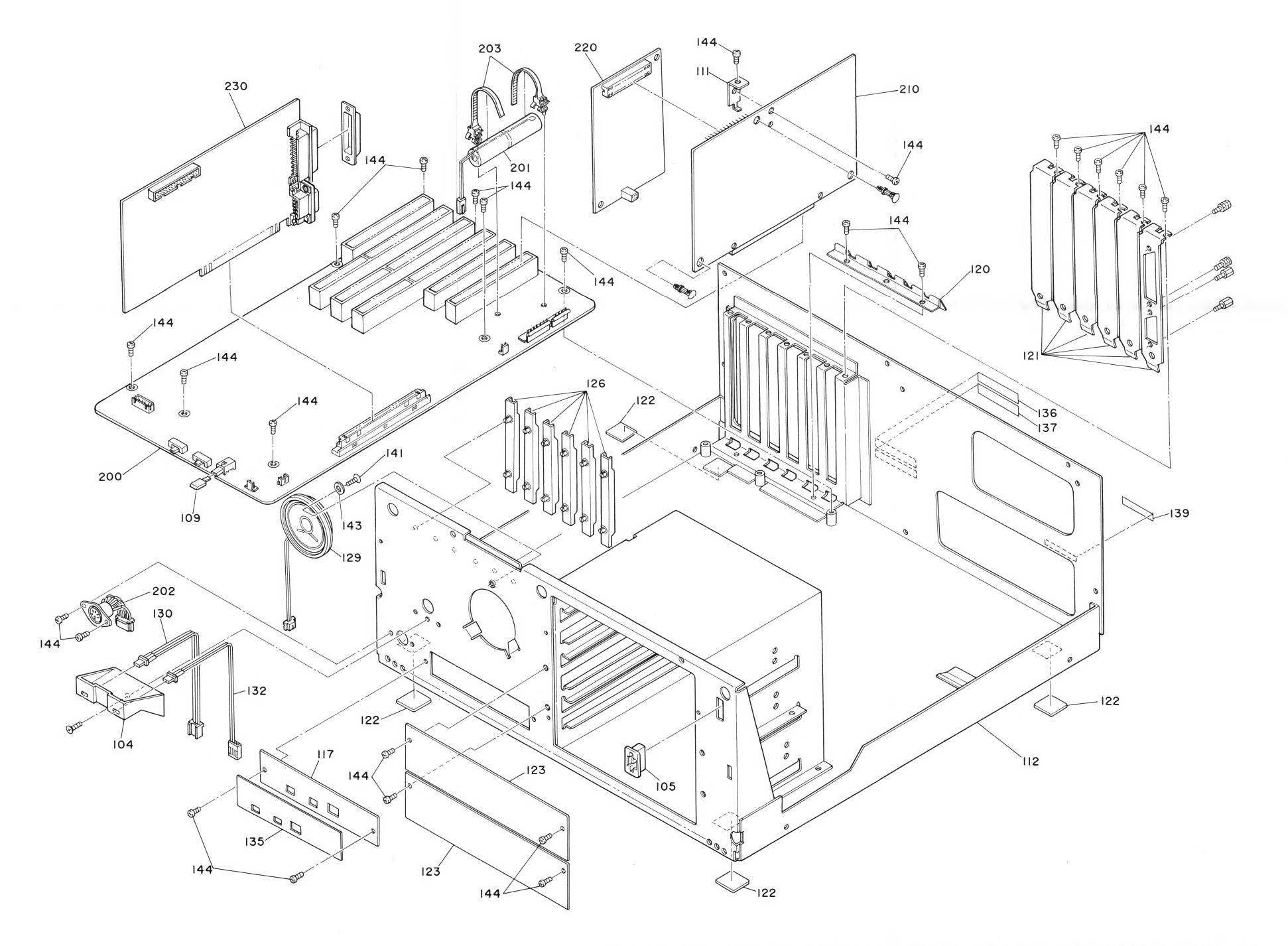

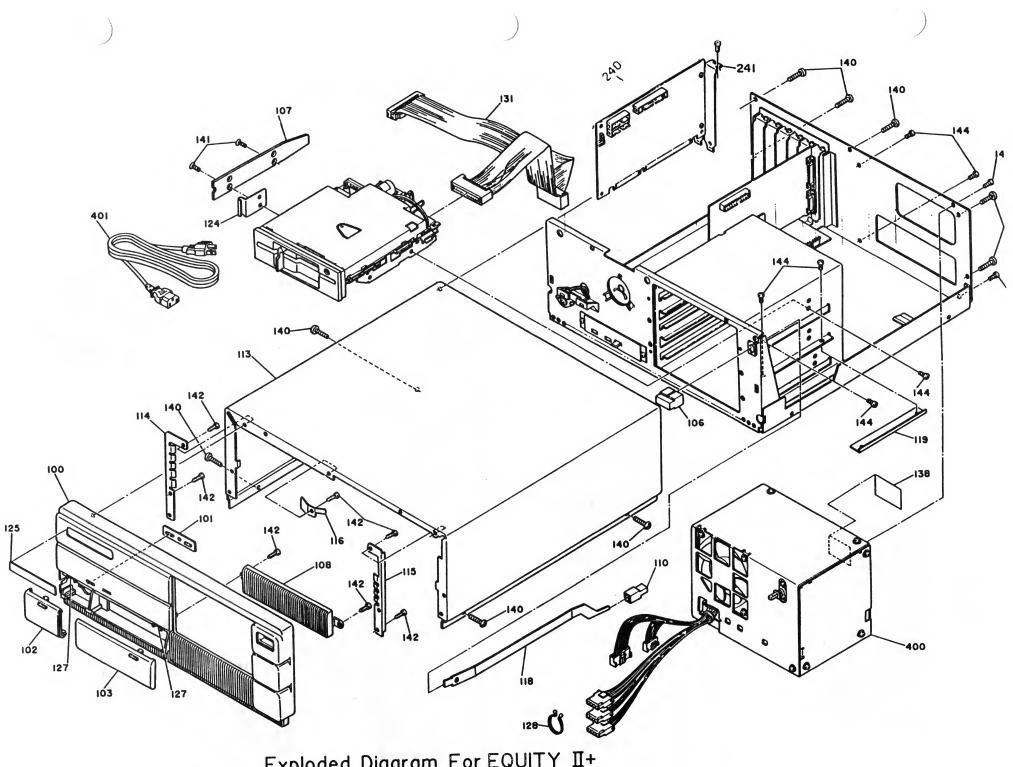

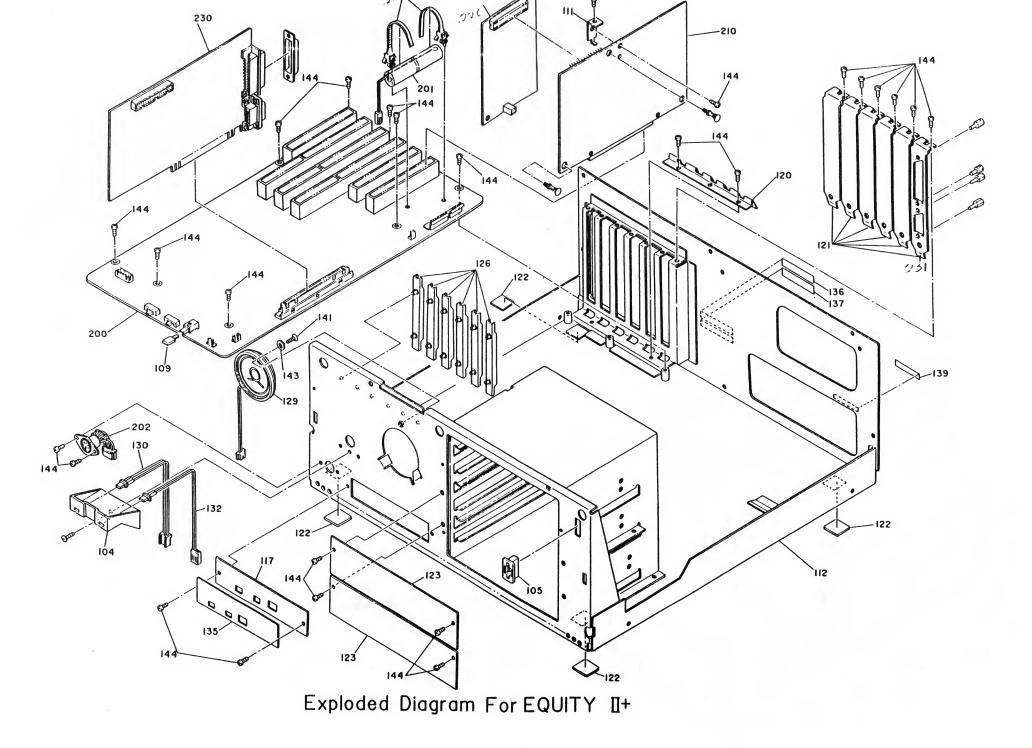

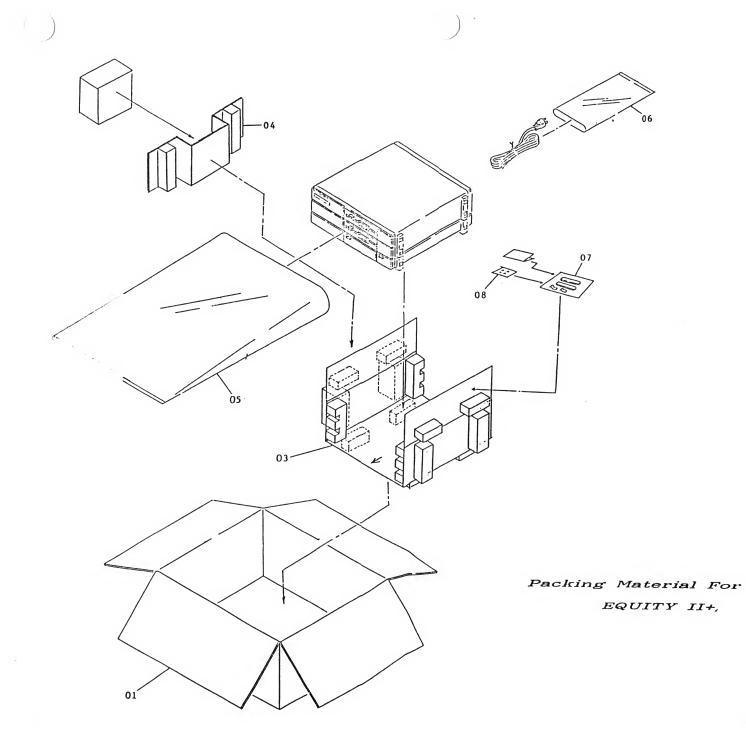

FIGURE 1-1. MAIN UNIT COMPONENT LOCATIONS

# **1.2 SPECIFICATIONS**

The following specifications apply to the complete system. Specifications for each of the major subassemblies follow this section.

| POWER SUPPLY                            |                                       |                  |

|-----------------------------------------|---------------------------------------|------------------|

| Input Voltage (Switchable)              |                                       |                  |

| U.S.                                    |                                       |                  |

| Rated                                   | 115V AC                               |                  |

| Valid                                   | 95V - 137V AC                         |                  |

| Europe                                  |                                       |                  |

| Rated                                   | 230V                                  |                  |

| Valid                                   | 195V – 265V AC                        |                  |

| Frequency, Valid                        | 47Hz – 63Hz                           |                  |

| Power Consumption                       | 110W Typical, 140W M                  |                  |

| Inrush Current                          | 32A or less, for 1/2 C                | Cycle, Maximum   |

| Output                                  |                                       |                  |

| 12V                                     | +12V : 4.5A                           | – 12V : 0.3A     |

| 5V                                      | +5V : 10A                             | -5V : 0.3A       |

| INSULATION STRENGTH                     |                                       |                  |

| Primary – Secondary                     | 1,500V AC for 1 minut                 | te               |

| Primary – Frame Ground                  | 1,500V AC for 1 minut                 | te               |

| Secondary – Frame Ground                | 500V AC for 1 minute                  |                  |

| INSULATION RESISTANCE                   |                                       |                  |

| Primary – Secondary                     | 50MΩ Min. (500V DC)                   |                  |

| Secondary – Frame Ground                | 50MΩ Min. (500V DC)                   |                  |

| Secondary – Frame Ground                | 50MΩ Min. (500V DC)                   |                  |

| MAXIMUM ENVIRONMENTAL CONDITIONS        | Operating                             | Non – Operating  |

| Ambient Temperature                     |                                       |                  |

| Ambient Temperature<br>Humidity         | 5 <sup>°</sup> c to 35 <sup>°</sup> c | – 20°c to 60°c   |

| Relative (non – condensing)<br>Wet Bulb | 20% to 80%                            | 10% to 90%       |

| Standard Model                          | 29 <sup>°</sup> c                     | 40°c             |

| Enhanced Model                          | 26°C                                  | 29°c             |

| Altitude (atmospheric pressure)         | 20 0                                  | 20 0             |

| Standard Model                          | 0m to 10,000m                         | 0m to 10,000m    |

| Enhanced Model                          | 0m to 3,000m                          | 0m to 10,000m    |

| SHOCK RESISTANCE, MAXIMUM               | 1G, 10ms                              | 3G, 10ms         |

| VIBRATION RESISTANCE, MAXIMUM           |                                       |                  |

| Standard Model                          | 0.2G, 5 to 150Hz                      | 1G, 5 to 150Hz   |

| Enhanced Model                          | 0.2G, 5 to 150Hz                      | 0.5G, 5 to 150Hz |

|                                         |                                       |                  |

## 1.2.1 MAIN UNIT SPECIFICATIONS

| DIMENSIONS<br>Height<br>Width<br>Depth<br>Weight (1 FDD Model) | 6.10" (155mm)<br>15.75" (400mm)<br>16.26" (413mm)<br>19.8lbs. (9 Kg)                                                                                                                                                                                                                     |

|----------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MICROPROCESSOR                                                 | 80286                                                                                                                                                                                                                                                                                    |

| COPROCESSOR (Optional)                                         | 80287 – 8                                                                                                                                                                                                                                                                                |

| BASIC INPUT/OUTPUT SYSTEM (BIOS)                               | AT - compatible: 2 128K - bit EPROM chips                                                                                                                                                                                                                                                |

| SYSTEM CLOCK SPEED                                             | 10MHz or 8MHz (hardware switchable)                                                                                                                                                                                                                                                      |

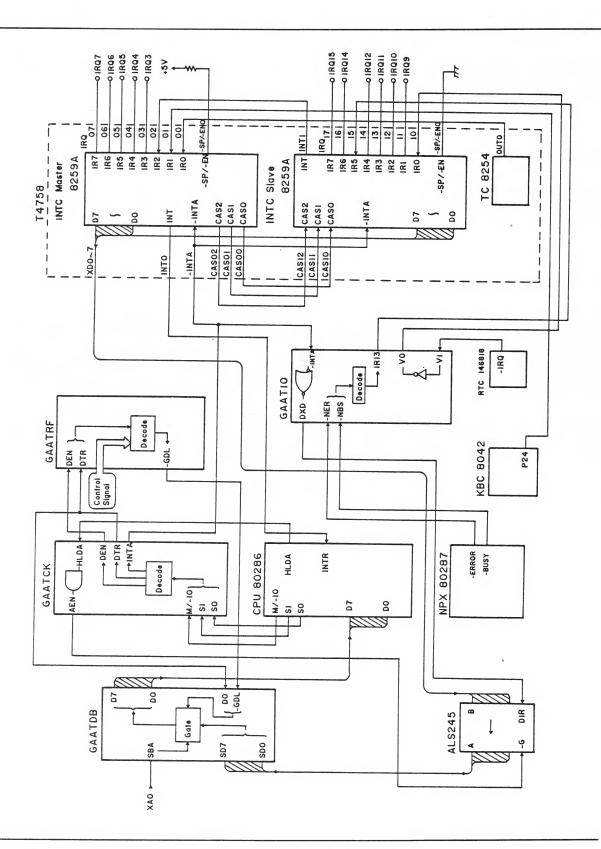

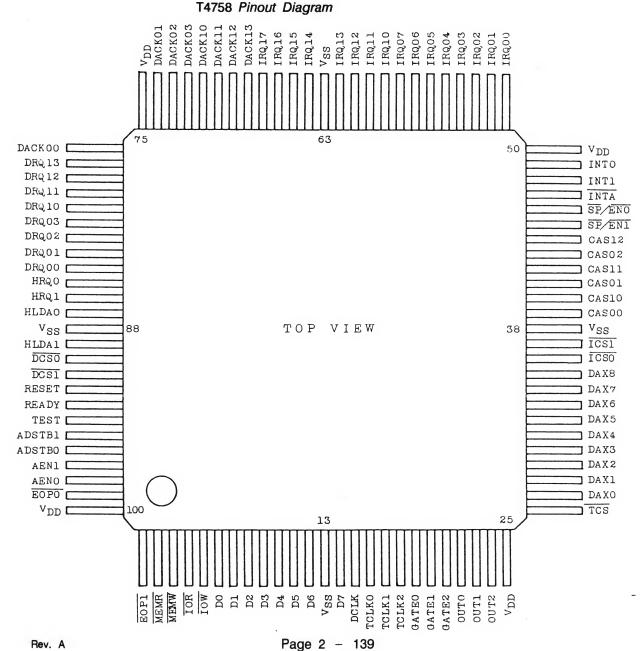

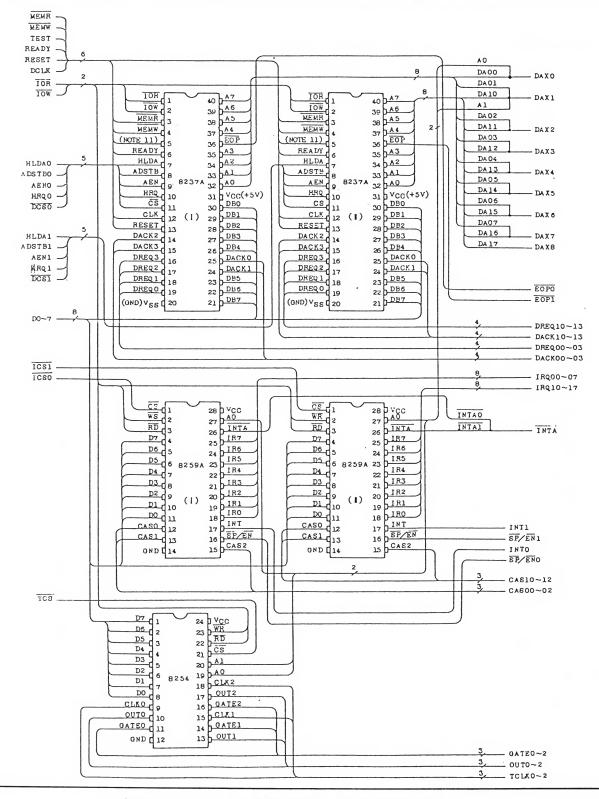

| SYSTEM SUPPORT CHIPS                                           | <ul> <li>T4758 - Includes functions of:</li> <li>2 Direct Memory Access Controllers (DMAC)<br/>(Intel 8237A - 5 compatible)</li> <li>2 Interrupt Controllers, (INTC)<br/>(Intel 8259A compatible)</li> <li>1 Timer/Counter<br/>(Intel 8254 - 2 compatible)</li> </ul>                    |

| Seiko Epson AT – Chipset                                       | Custom gate arrays providing: data – and address –<br>bus control; system clock and timing control;<br>memory address, refresh, and timing generation;<br>miscellaneous system support circuitry.                                                                                        |

| KEYBOARD INTERFACE                                             | 8042 – based Enhanced (101/102 – key) Keyboard –<br>compatible Interface, plug – compatible with IBM<br>Enhanced or Standard PC AT Keyboard.                                                                                                                                             |

| SERIAL COMMUNICATIONS INTERFACE                                | RS-232C serial interface (9-pin D-shell)                                                                                                                                                                                                                                                 |

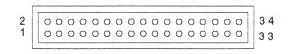

| PARALLEL INTERFACE                                             | Centronics - compatible parallel printer interface                                                                                                                                                                                                                                       |

| EXPANSION BUS INTERFACE                                        | <ul> <li>3 8 - bit PC - compatible expansion slots <ul> <li>(1 used by Multi - Function card, 2 open)</li> </ul> </li> <li>3 16 - bit AT - compatible expansion slots <ul> <li>(Enhanced Model: 1 used for HDC, 2 open)</li> </ul> </li> </ul>                                           |

| MASS STORAGE SLOTS                                             | 3 Half-height drive bays. (May be configured by                                                                                                                                                                                                                                          |

| MASS STORAGE<br>Standard Model                                 | user as 1 full – height and 1 half – height.)<br>1 5.25" high – density double – sided floppy disk drive<br>(1.2MB formatted capacity)                                                                                                                                                   |

| Enhanced Model                                                 | <ol> <li>5.25" 1.2MB floppy disk drive (same as above)</li> <li>One of the following:         <ol> <li>Half – height 3.5" 20MB 65ms Hard Disk Drive</li> <li>Half – height 5.25" 40MB 28ms Hard Disk Drive</li> <li>Half – height 5.25" 40MB 40ms Hard Disk Drive</li> </ol> </li> </ol> |

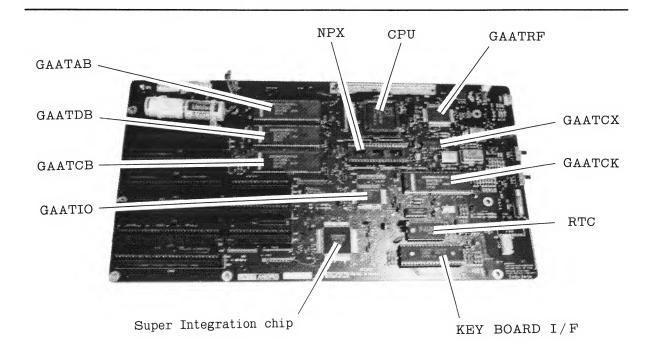

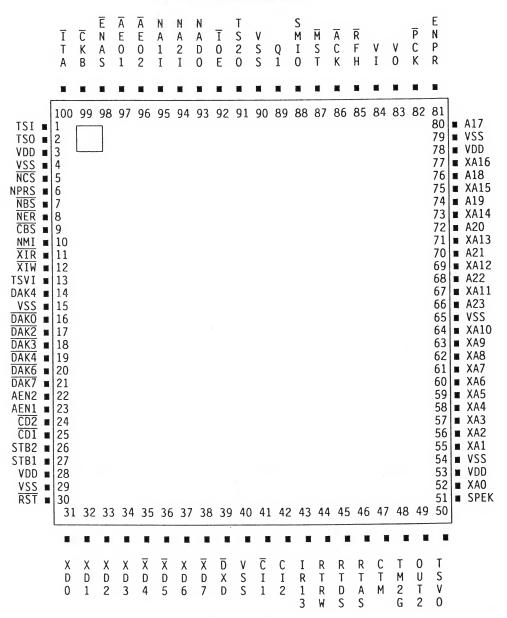

| Name                      | Model      | Location | Function                                                                                                                                                   |

|---------------------------|------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CPU                       | 80286 - 10 | 6C       | 16 bit CPU                                                                                                                                                 |

| NPX                       | 80287 - 8  | 5C       | Co-processor (socket only)                                                                                                                                 |

| Super Integration<br>Chip | T4758      | 1B       | DMA control, Interrupt control, counter/timer                                                                                                              |

| RTC                       | 146818     | 2D       | System clock, calender and CMOS RAM                                                                                                                        |

| KEYBOARD I/F              | 8042       | 1D       | Interface between 80286 and keyboard                                                                                                                       |

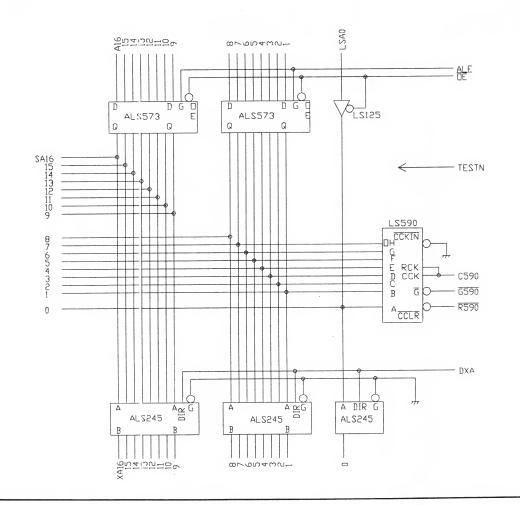

| GAATAB                    | E01085CB   | 6A       | Controls CPU address bus $(A16-0)$ , system address bus $(SA16-0)$ and internal address bus $(XA16-0)$ .<br>Generates refresh address.                     |

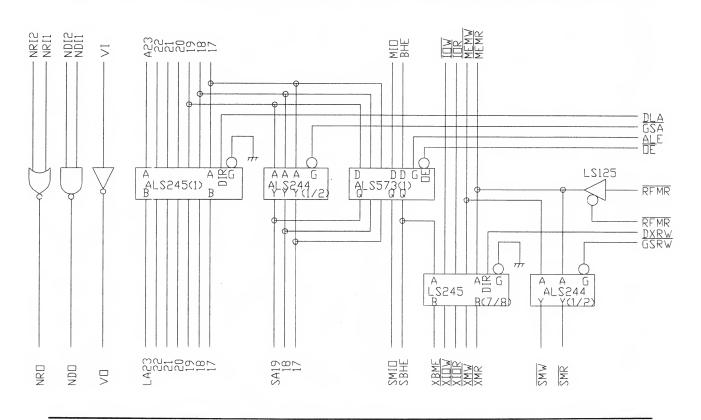

| GAATCB                    | E01086CA   | 4A       | Control bus (I/O write pulse, I/O read pulse,<br>memory write pulse, memory read pulse) and 7 MSB<br>of address bus (A23 – 17) and bus high enable signal. |

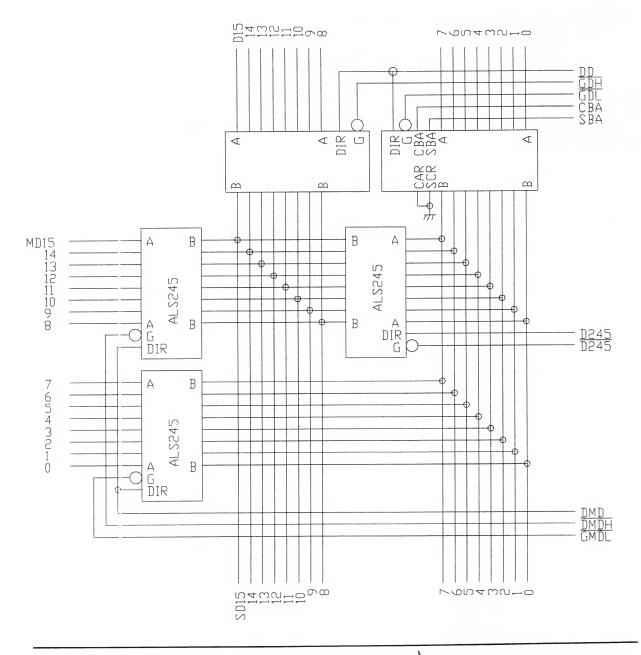

| GAATDB                    | E01068CA   | 5A       | Control CPU bus $(D15-0)$ , system data bus $(SD15-0)$<br>and memory data bus $(MD15-0)$                                                                   |

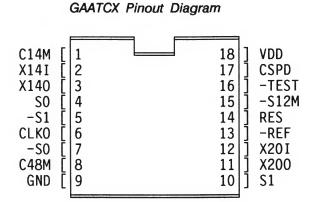

| GAATCK                    | E01068CA   | 4D       | Clock generator, bus controller and shut down circuit.                                                                                                     |

| GAATCX                    | E01117BA   | 5D       | Clock generator, Clock selector                                                                                                                            |

| GAATRF                    | E01069BB   | 6D       | Controls D-RAM refresh, DMA transfer, 16-8 data bit conversion, and wait state insertion.                                                                  |

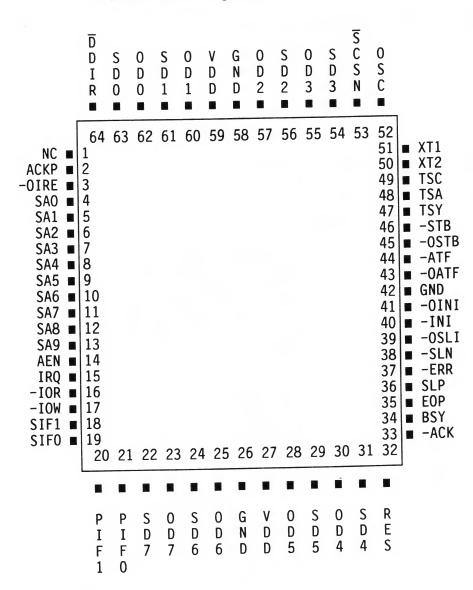

| GAATIO                    | E01092EA   | зC       | Address decoder for I/O space and I/O registers.                                                                                                           |

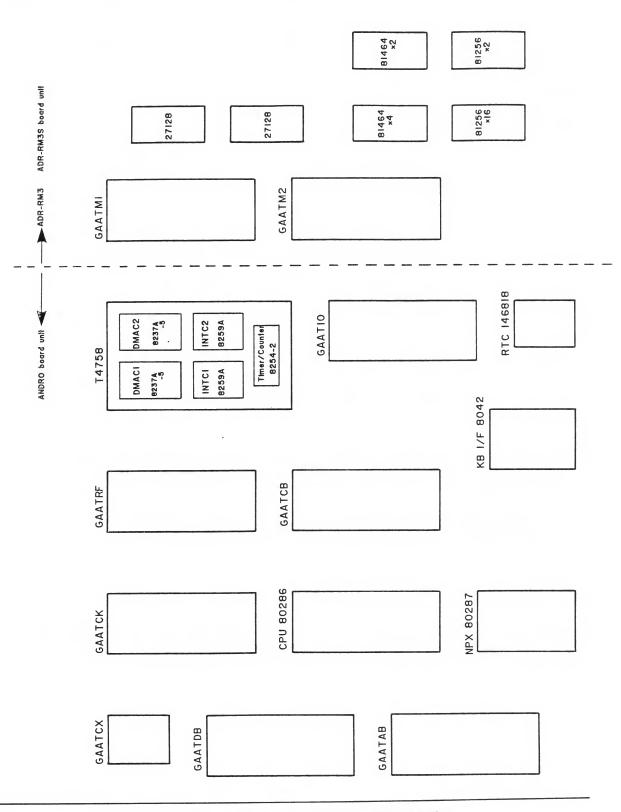

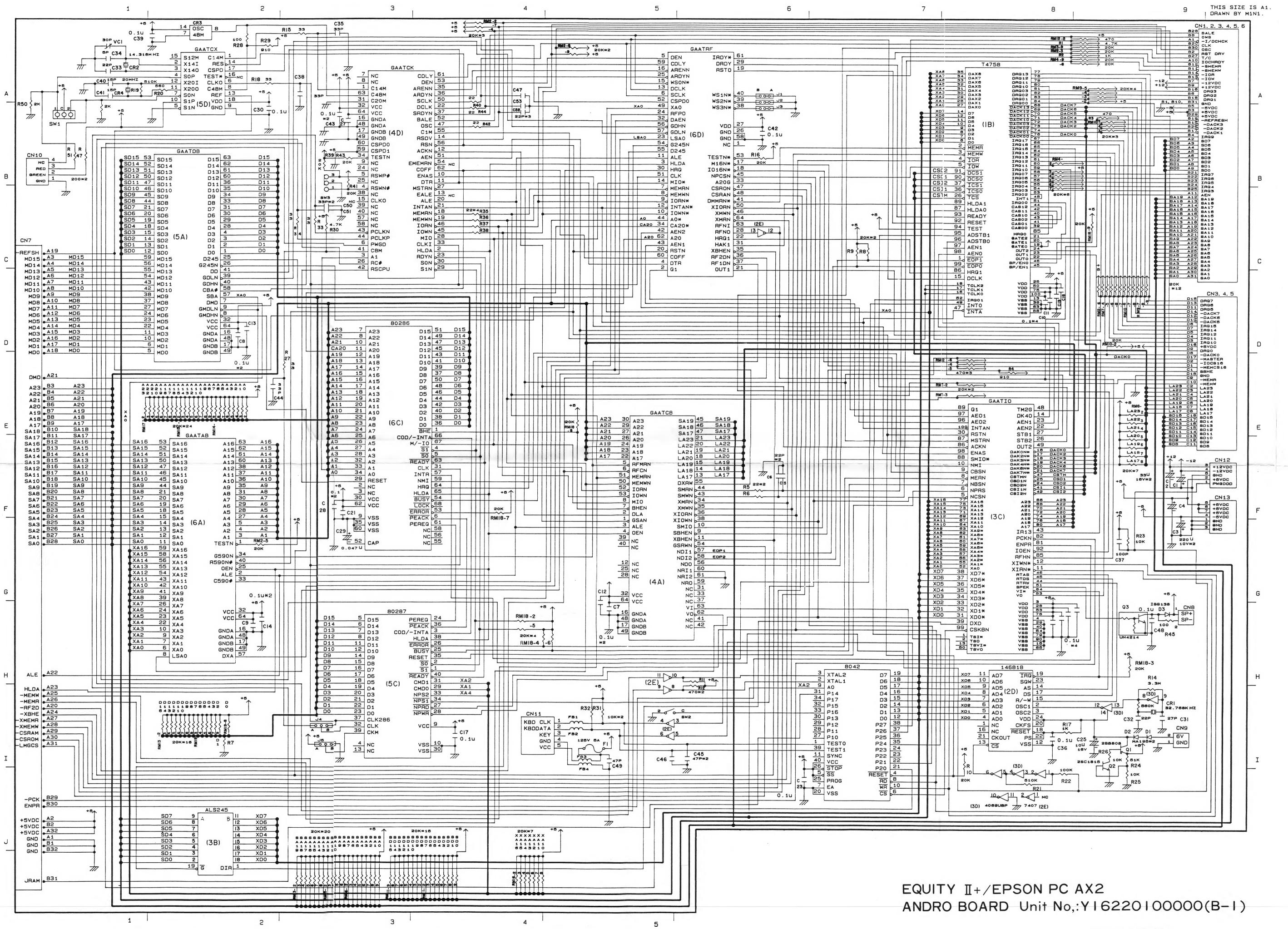

#### TABLE 1-1. ANDRO BOARD COMPONENT DESCRIPTION

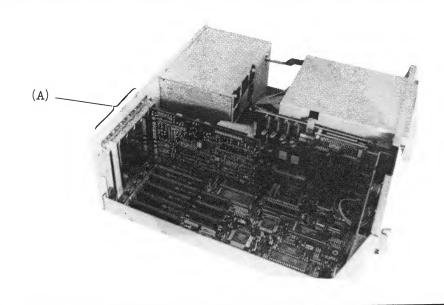

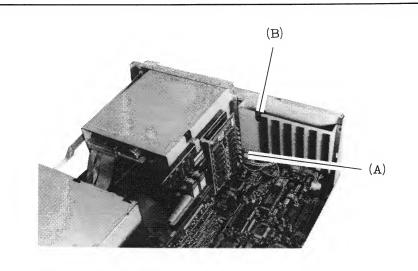

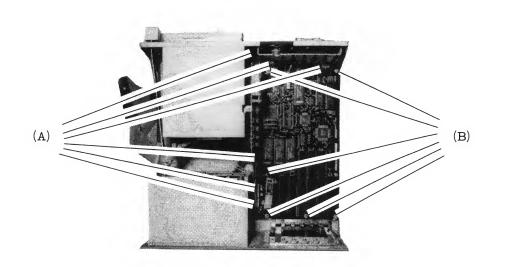

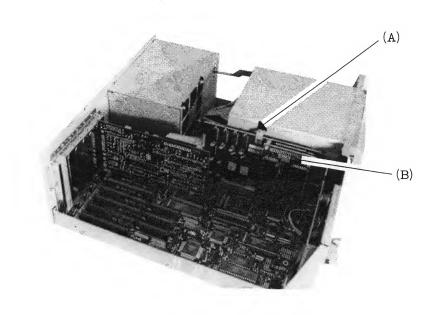

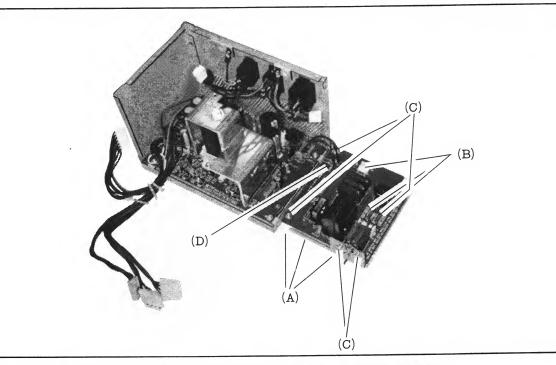

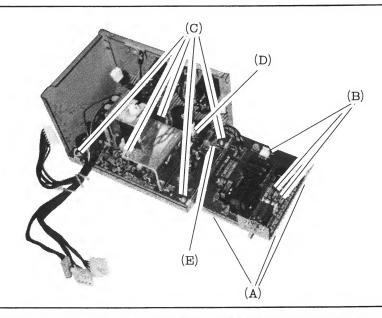

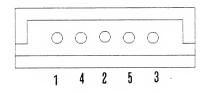

FIGURE 1-2. COMPONENT LOCATIONS ON MAIN CONTROL BOARD

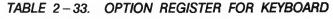

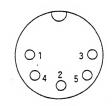

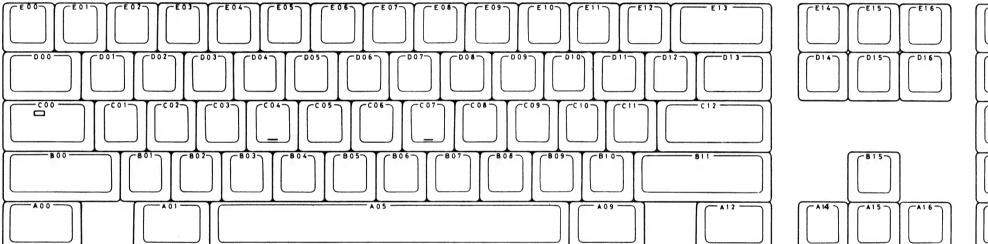

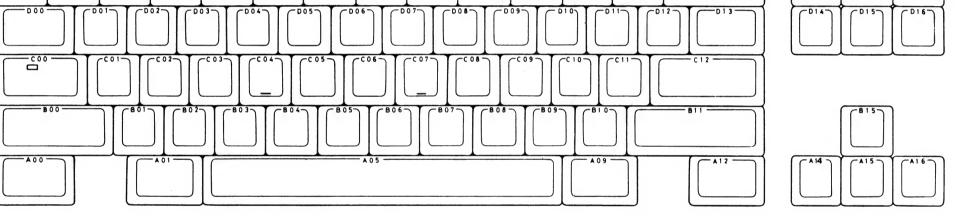

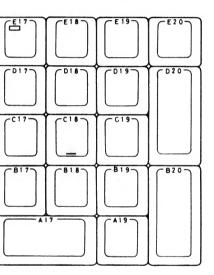

## 1.2.2 KEYBOARD SPECIFICATIONS

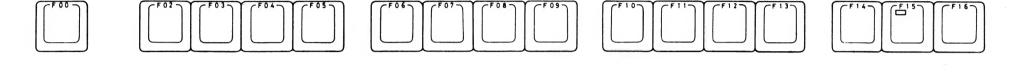

LAYOUT CORD STATUS INDICATORS

CONNECTOR

WEIGHT DIMENSIONS 101 – key (102 in Europe) "Enhanced" keyboard 60cm (23.6") 5 – wire, coiled, unshielded cable LED indicators, controlled by commands from the Main Unit, for "Num Lock" "Scroll Lock" and "Caps Lock". Main Unit end: 5 – pin, "O" – shell (IBM plug compatible) Keyboard end: 5 – wire "modular" cable jack (Epson proprietary)

3.02lbs (1.37Kg) Width: 19.3" (49cm) Depth: 7.8" (19.75cm) Height: 1.9" (4.77cm)

# EPSON-

### 1.2.3 FLOPPY DISK DRIVE SPECIFICATIONS

#### 1.2.3.1 1.2MB FLOPPY DISK DRIVE SPECIFICATIONS

NEC model FD1155C, FD1157C; Cannon MD5501 MODEL NUMBER 1.2MB Formatted: 1.6MB Unformatted; CAPACITY DATA TRANSFER RATE 500Kbps Max.; 300Kbps optional. STEP RATE (Track - to - track seek) 3ms HEAD SETTLE TIME 15ms. Minimum HEAD LOADING TIME 35ms, Minimum MOTOR START TIME 800ms, Minimum MOTOR SPEED 360 rpm **CYLINDERS** 80 TRACKS 160 (80 cylinders x 2 heads) CURRENT REQUIREMENTS At "Motor On" Typical 390mA 210mA +12V460mA + 5V 460mA POWER CONSUMPTION 4.8 Watts DIMENSIONS (14.6cm) Width: 5.75" (20.3cm) Depth: 8" Height: 1.61" (4.1 cm)Non - Operating ENVIRONMENTAL CONDITIONS Operating 4° to 46° c -20° to 65°c Temperature 10% to 90% Relative Humidity (non-condensing) 20% to 80% 30°c 15°c Temperature Change (per hour) Vibration (x, y or z axis) 100Hz 100Hz

10G

15G

Rev. A

Shock(x, y or z axis)

#### 1.2.3.2 720KB 3.5" FLOPPY DISK DRIVE (OPTIONAL)

MODEL NUMBER CAPACITY DATA TRANSFER RATE DATA ACCESS TIME STEP RATE (Track - to - track seek) HEAD SETTLE TIME HEAD LOADING TIME MOTOR START TIME MOTOR SPEED CYLINDERS TRACKS Seiko Epson SMD – 489M 720KB Formatted; 1000KB Unformatted 250Kbps 100ms, average 3ms 15ms 15ms 500ms 300rpm 80 160 (80 x 2 heads)

#### CURRENT REQUIREMENTS

+ 5V

#### POWER CONSUMPTION

DIMENSIONS

#### ENVIRONMENTAL CONDITIONS

Operating

Height: 1.0"

Weight: 1.3 lbs.

Reading

360mA

1.8W

Width:

Depth:

#### Non - Operating

Maximum

1.0A

(10.2cm)

(15.0cm)

(25.4cm)

(585g)

Temperature Relative Humidity (non – condensing) Vibration (x, y or z axis) Shock (x, y or z axis) 4°c to 45°c 20% to 80% 5 to 500Hz, 0.6G 5G

4.0"

5.9"

- 20°c to 65°c 95% maximum 5 to 500Hz, 3G 50G

## 1.2.3.3 360K 5.25" FLOPPY DISK DRIVE (OPTIONAL)

| MODEL NUMBER<br>CAPACITY<br>DATA TRANSFER RATE<br>STEP RATE (Track – to – track seek)<br>HEAD SETTLE TIME<br>HEAD LOADING TIME<br>MOTOR START TIME<br>MOTOR SPEED<br>CYLINDERS<br>TRACKS | Cannon MD52<br>Formatted: 36<br>250KB/sec<br>6ms<br>15ms<br>95ms<br>500ms<br>300rpm<br>40<br>80 (40/side) |                | rmatted: 500KB                                                                                           |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|----------------|----------------------------------------------------------------------------------------------------------|

| CURRENT REQUIREMENTS                                                                                                                                                                     | Peak                                                                                                      | Typical        | Maximum                                                                                                  |

| + 12V<br>+ 5V                                                                                                                                                                            | 1.310A<br>-                                                                                               | 250mA<br>140mA | 460mA<br>180mA                                                                                           |

| POWER CONSUMPTION (Typical)                                                                                                                                                              | Reading                                                                                                   | Writing        | Waiting                                                                                                  |

|                                                                                                                                                                                          | 2.75W                                                                                                     | 3.61W          | 0.87W                                                                                                    |

| DIMENSIONS                                                                                                                                                                               | Width: 5.8"<br>Depth: 7.8"<br>Height: 1.7"                                                                | (19.8cm)       |                                                                                                          |

| ENVIRONMENTAL CONDITIONS                                                                                                                                                                 | <b>Oper</b> ating                                                                                         |                | Non – Operating                                                                                          |

| Temperature<br>Relative Humidity (non – condensing)<br>Vibration<br>Shock                                                                                                                | 5°c to 45°c<br>20% to 80%<br>< 1G, 10Hz<br>< 5G                                                           |                | <ul> <li>− 22°c to 60°c</li> <li>10% to 90%</li> <li>&lt; 3G, 10Hz to 100Hz</li> <li>&lt; 50G</li> </ul> |

5

## 1.2.4 HARD DISK DRIVE SPECIFICATIONS

#### 1.2.4.1 20MB HALF-HEIGHT HARD DISK DRIVE (OPTIONAL)

MODEL NUMBER Seiko Epson HMD - 720 CAPACITY DATA TRANSFER RATE 5Mbps DATA ACCESS TIME STEP RATE (Track - to - track seek) **CYLINDERS** 615 TRACKS 2460 (615 x 4 heads) SECTORS/TRACK 32 MOTOR SPEED 3,528 rpm (±01%) INTERFACE ST-506/412

CURRENT REQUIREMENTS

+12V+5V

#### POWER CONSUMPTION

DIMENSIONS

#### ENVIRONMENTAL CONDITIONS

Temperature Relative Humidity (non-condensing) Altitude (atmospheric pressure) Vibration

Shock

20MB Formatted; 25.5MB Unformatted 69ms, average (includes Head Settle Time) 18ms, average (includes Head Settle Time)

Average

580mA

200mA

#### Maximum

770mA 360mA

8.0 Watts

Width: 5.8" (14.6cm) Depth: 7.8" (19.8 cm)Height: 1.6" (4.1 cm)Weight: 2.7 lbs (1.23Kg)

#### Operating

#### Non - Operating

4° to 50°c 8% to 85% 3.000m 5 to 36Hz: 0.15mm 36 to 500Hz: 0.4G 8G, 10ms

-40° to 65°c 8% to 85% 10.000m 5 to 12Hz: 10.2mm 13 to 500Hz: 3.0G 40G, 10ms

#### 1.2.4.2 40MB HALF-HEIGHT 28MS HARD DISK DRIVE (OPTIONAL)

| MODEL NUMBER<br>CAPACITY<br>DATA TRANSFER RATE<br>DATA ACCESS TIME<br>STEP RATE (Track – to – track seek)<br>MOTOR SPEED<br>HEADS<br>CYLINDERS<br>TRACKS | CDC 94205 - 51<br>42MB Formatted; 50.24M<br>5Mbps<br>28ms, average (includes<br>5ms, average (includes H<br>3,597rpm (±0.5%)<br>5<br>989<br>4,945 (989 x 5 sides)                          | Head Settle Time                                                                                   |

|----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|

| CURRENT REQUIREMENTS                                                                                                                                     | Typical Maximum                                                                                                                                                                            | Start – up                                                                                         |

| + 12V<br>+ 5V                                                                                                                                            | 1.5A 2.0A<br>400mA 600mA                                                                                                                                                                   | 4.5A<br>1.0A                                                                                       |

| POWER CONSUMPTION                                                                                                                                        | 20 Watts                                                                                                                                                                                   |                                                                                                    |

| DIMENSIONS                                                                                                                                               | Width:         5.75"         (14.600)           Depth:         8.1"         (20.570)           Height:         1.625"         (4.13cr)           Weight:         3.8 lbs.         (1.73Kg) | cm)<br>n)                                                                                          |

| ENVIRONMENTAL CONDITIONS                                                                                                                                 | Operating                                                                                                                                                                                  | Non – Operating                                                                                    |

| Temperature<br>Relative Humidity (non – condensing)<br>Temperature Change (per hour)<br>Vibration (x, y or z axis)<br>Shock (x, y or z axis)             | 10° to 50°c<br>8% to 80%<br>10°c<br>5 to 22Hz, 0.5mm<br>22 to 500Hz, 0.5G Max.<br>2G, 10ms Max.                                                                                            | 14° to 130°c<br>8% to 90%<br>20°c<br>5 to 22Hz, 0.5mm<br>22 to 500Hz, 0.75G Max.<br>40G, 10ms Max. |

# EPSON-

#### 1.2.4.3 40MB HALF - HEIGHT 40MS HARD DISK DRIVE (OPTIONAL)

MODEL NUMBER CAPACITY DATA TRANSFER RATE STEP RATE (Track – to – track seek) DATA ACCESS TIME MOTOR SPEED CYLINDERS TRACKS HEADS Tokico TD 5046 40.3MB Formatted; 50.92 Unformatted 5Mbps 8ms 40ms Average (includes Head Settle Time) y3,550rpm 615 4920 (615 x 8) 8

> (14.9cm) (20.8cm)

(4.3cm)

(1.8Kg)

CURRENT REQUIREMENTS

+ 12V + 5V

POWER CONSUMPTION DIMENSIONS

#### ENVIRONMENTAL CONDITIONS

Operating

26.6 Watts

Depth: 8.19" Height: 1.69"

Weight: 4lbs.

5.87"

Width:

Typical

1.8A

1A

Non - Operating

Power-On

3.5A

Temperature Temperature Change (per hour) Relative Humidity (non – condensing) Vibration (x, y or z axis) Shock(x, y or z axis) 5<sup>°</sup> to 45<sup>°</sup>c 10<sup>°</sup>c/h 5% to 80% 0.25G Max. 2G Max. - 20° to 60°c 10°c/h 5% to 90% 2G Max. 20G Max.

# **CHAPTER 2**

# **PRINCIPLES OF OPERATION**

## TABLE OF CONTENTS

| Section        | Title                                         | Page   |

|----------------|-----------------------------------------------|--------|

| 2.1            | SYSTEM OVERVIEW                               | . 2-1  |

| 2.2<br>2.2.1   | ADRPS POWER SUPPLY UNIT                       |        |

| 2.2.2          | Primary – side Circuit                        |        |

| 2.3            | ANDRO Board Main Control Operations           |        |

| 2.3.1          | System Clock Generation Circuit               | . 2-12 |

| 2.3.2          | System Reset Signal Generation                |        |

| 2.3.3          | Internal Memory Control Circuit               |        |

| 2.3.4<br>2.3.5 | Byte/Word Access & 16 – 8 Bit Data Conversion | . 2-21 |

| 2.3.5          |                                               |        |

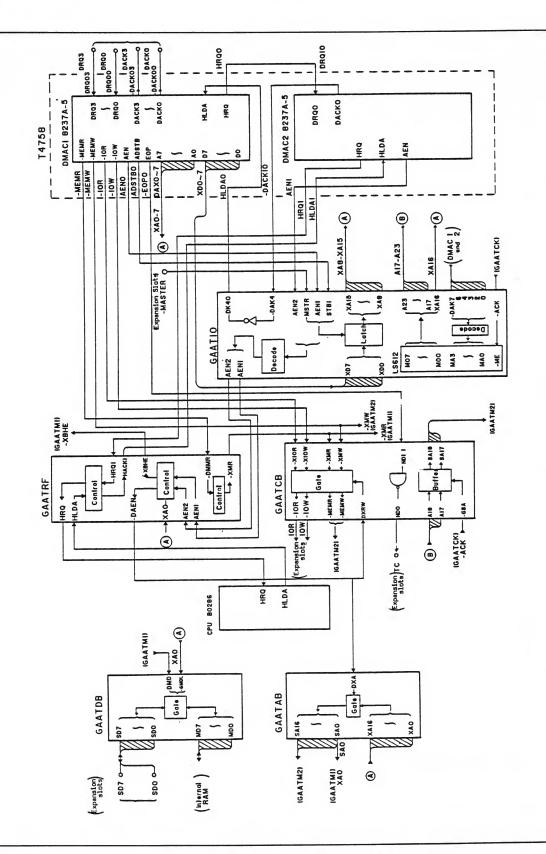

| 2.3.0          | DMA Control Circuit                           |        |

| 2.3.8          | Ready Signal Control Circuit                  |        |

| 2.3.9          |                                               |        |

| 2.3.10         | ROM Access Circuit                            |        |

| 2.3.11         | DRAM Refresh Circuit                          |        |

| 2.3.12         | RAM Parity Check Circuit                      |        |

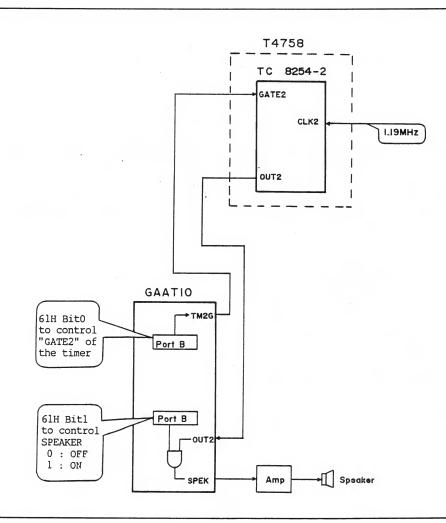

| 2.3.13         | Speaker Control Circuit                       |        |

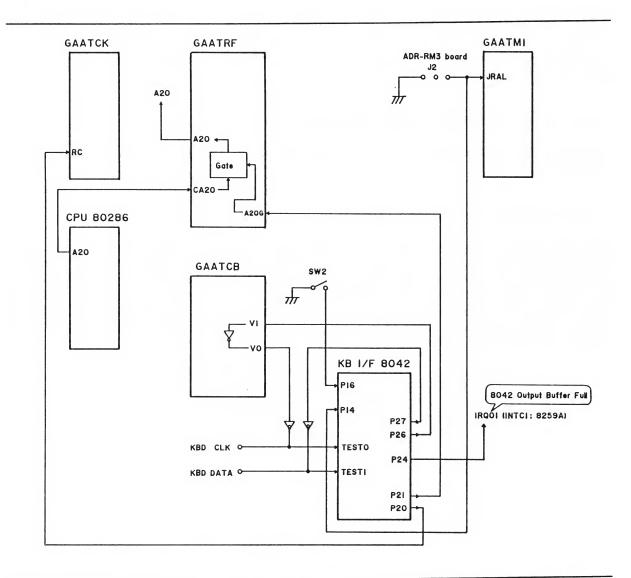

| 2.3.14         | Keyboard Interface And Other Circuits         |        |

| 2.3.15         | I/O Slot Access Signals                       |        |

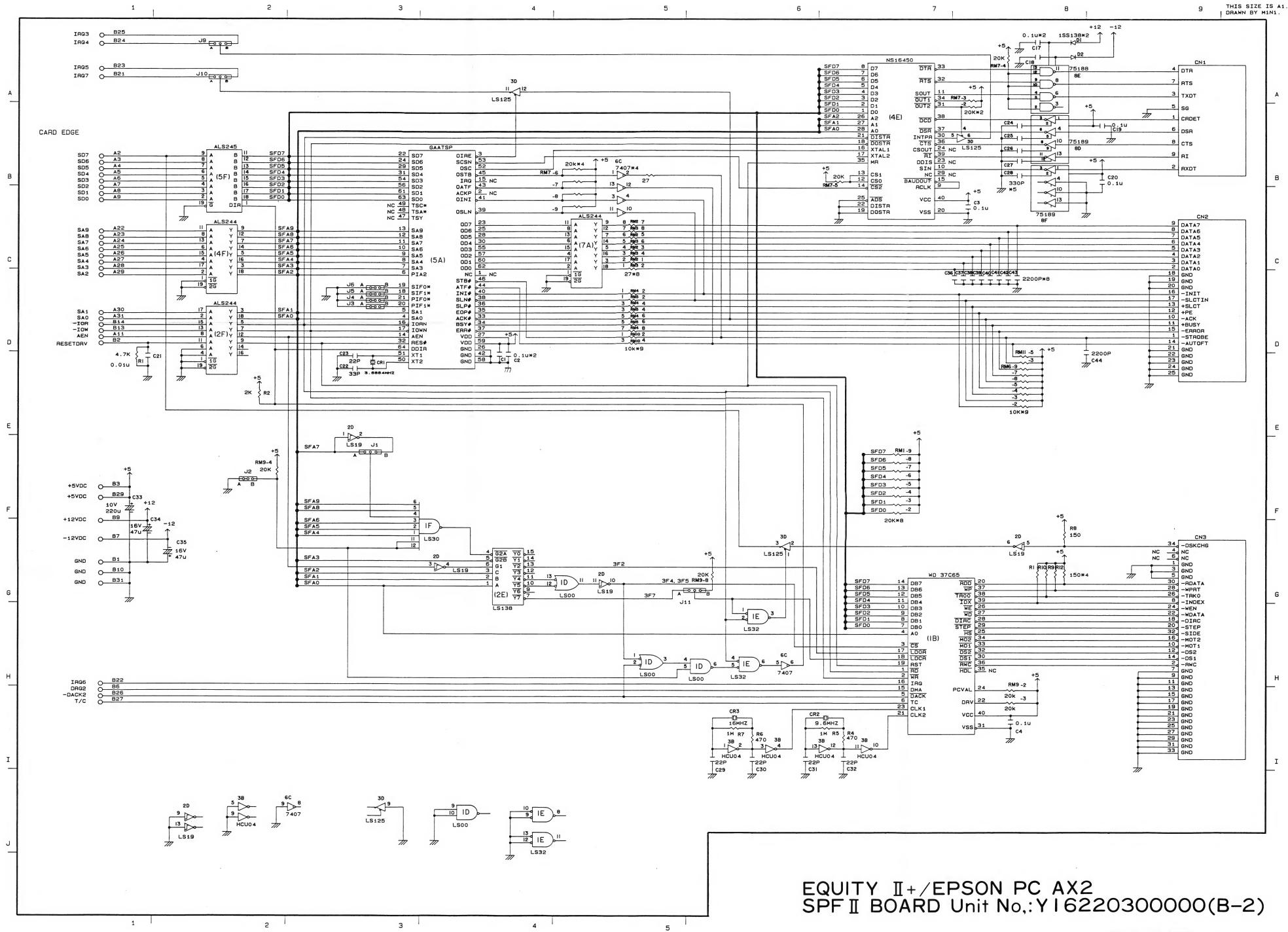

| 2.4            | MULTI – FUNCTION ADAPTER (SPF2 BOARD)         |        |

| 2.4.1          | Serial Interface                              |        |

| 2.4.2          | Parallel Communications Control Circuit       |        |

| 2.4.3          | Floppy Disk Controller                        | . 2–59 |

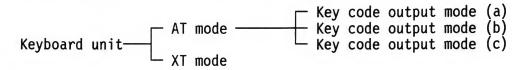

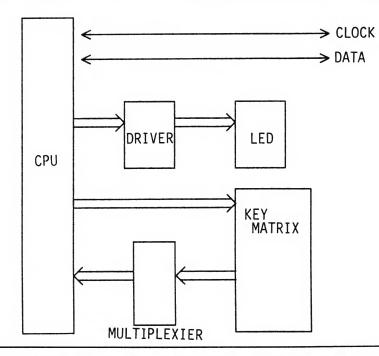

| 2.5            | KEYBOARD                                      | 2-64   |

| 2.5.1          | Block Diagram                                 |        |

| 2.5.2          | Interface Signals                             |        |

| 2.5.3          | Description of Interface Signals (AT mode)    |        |

| 2.5.4          | Interface Circuit Specification               | 2 - 69 |

| 2.5.5          | Connector Pin Explanation                     | 2 - 70 |

| 2.5.6          | Function Specifications                       |        |

| 2.5.7          | Key Scan Code                                 |        |

| 2.5.8          | Commands (AT mode)                            |        |

| 2.5.9          | Scan Codes                                    | 2-84   |

| 2.6    | GATE ARRAYS SPECIFICATION |

|--------|---------------------------|

| 2.6.1  | GAATAB                    |

| 2.6.2  | GAATCB                    |

| 2.6.3  | GAATDB                    |

| 2.6.4  | GAATCK                    |

| 2.6.5  | GAATM2                    |

| 2.6.6  | GAATIO                    |

| 2.6.7  | GAATM1                    |

| 2.6.8  | GAATRF                    |

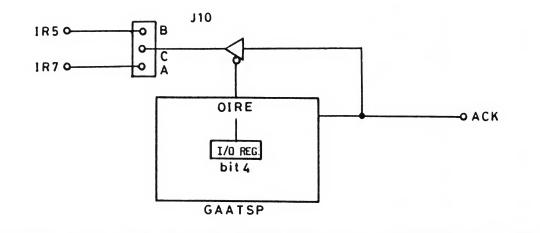

| 2.6.9  | GAATSP                    |

| 2.6.10 | GAATCK                    |

| 2.6.11 | WD37C65                   |

| 2.6.12 | NS16450                   |

| 2.6.13 | T4758                     |

|        |                           |

## LIST OF FIGURES

| Figure | Title                                        | Page   |

|--------|----------------------------------------------|--------|

| 2-1    | System Configuration Block Diagram           | 2 – 1  |

| 2-2    | Power Supply Block Diagram                   | 2-2    |

| 2-3    | Line Noise Filter Circuit                    | 2-4    |

| 2-4    | Voltage Doubler Rectifier Circuit            | 2-5    |

| 2-5    | Switching Wave Generation Circuit            | 2-6    |

| 2-6    | + 12V Supply Circuit                         | 2-7    |

| 2 – 7  | + 5V Supply Circuit                          | 2-7    |

| 2-8    | - 12V/-5V Supply Circuit                     | 2-8    |

| 2-9    | Output - Voltage Stabilization Circuit       | 2-9    |

| 2 – 10 | Power - Down - Signal Generation Circuit     | 2 - 10 |

| 2-11   | Power Down Timing Chart                      | 2-11   |

| 2-12   | Internal Circuit Configuration               | 2 - 13 |

| 2 - 13 | System Clock Generation Circuit              | 2 - 14 |

| 2-14   | Clock Speed Selection                        | 2 - 15 |

| 2 - 15 | System Reset Signal Circuit                  | 2 - 17 |

| 2-16   | Internal Memory Control Circuit              | 2 - 19 |

| 2 - 17 | RAM Chip Addresses of System Memory          | 2 - 20 |

| 2-18   | Byte/Word Access & 16-8 Bit Data Conversion  | 2 - 23 |

| 2-19   | Data Transmission to 16 Bit Device           |        |

|        | (Byte Transmission of Even Address)          | 2 - 25 |

| 2 - 20 | Data Transmission to 8 Bit Device            |        |

|        | (Byte Transmission of Even Address)          | 2-26   |

| 2-21   | Data Transmission to 8 Bit Device            |        |

|        | (Word Transmission of Even Address)          | 2 - 27 |

| 2 – 22 | Data Transmission to 8 Bit Device            |        |

|        | (Byte Transmission of Even Address)          | 2 - 28 |

| 2 – 23 | Data Transmission to 8 Bit Device Read Mode  | 2 20   |

|        | (Byte Transmission of Odd Address)           | 2 - 29 |

| 2 - 24 | Data Transmission to 8 Bit Device Write Mode | 2 20   |

|        | (Byte Transmission of Odd Address)           | 2 - 30 |

| 2 – 25 | Data Transmission to 8 Bit Device Read Mode  | 2 00   |

|        | (Word Transmission of Even Address)          | 2 - 31 |

| 2 - 26           | Data Transmission to 8 Bit Device Write Mode                                                                                                  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| 2-20             | (Word Transmission of Even Address)                                                                                                           |

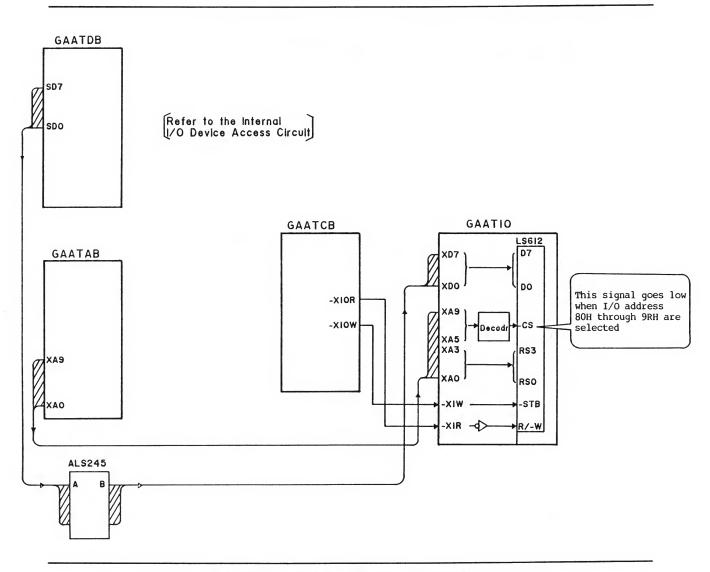

| 2-27             | I/O Device Access Circuit $\dots \dots \dots$ |

| 2-27             | Page Register Circuit                                                                                                                         |

| 2 - 29           | 8-Bit DMA (Internal Memory $< -> I/O$ )                                                                                                       |

| 2 - 30           | 8 – Bit DMA (Internal Memory $< ->$ Internal Memory)                                                                                          |

| 2-31             | 16 - Bit DMA (Internal Memory $< - > I/O$ )                                                                                                   |

| 2-32             | Ready Signal Control Circuit                                                                                                                  |

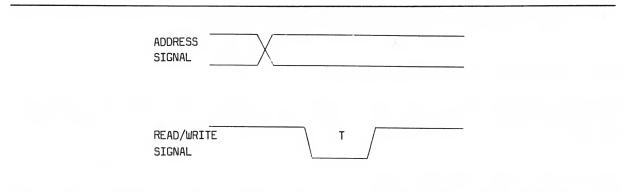

| 2 - 33           | Timing between Address Signal and Read/Write Signal                                                                                           |

| 2 - 34           | Command Delay Control Circuit                                                                                                                 |

| 2-35             | Interrupt Control Circuit                                                                                                                     |

| 2 - 36           | ROM Access Circuit                                                                                                                            |

| 2 - 37           | DRAM Refresh Circuit                                                                                                                          |

| 2-38             | RAM Parity Check Circuit Data Write                                                                                                           |

| 2-39             | RAM Parity Check Circuit Data Read                                                                                                            |

| 2-39             | Speaker Control Circuit                                                                                                                       |

| 2 - 40<br>2 - 41 | Keyboard & Other Circuits                                                                                                                     |

| 2 - 41<br>2 - 42 | I/O Slot Access Signals                                                                                                                       |

| 2 - 42           | 16450 Chip Select Circuit                                                                                                                     |

| 2 - 43<br>2 - 44 | I/O Address Selection                                                                                                                         |

| 2 - 44<br>2 - 45 | Data Output (Printer Data Register Write)                                                                                                     |

| 2 - 45<br>2 - 46 | Output Data Read Circuit                                                                                                                      |

| 2-40             | Printer Control Signal Output Circuit                                                                                                         |

| 2-47             | Printer Control Signal Read Circuit                                                                                                           |

| 2 - 48<br>2 - 49 | Printer Status Read Circuit                                                                                                                   |

| 2 - 49           | Interrupt Signal Control Circuit                                                                                                              |

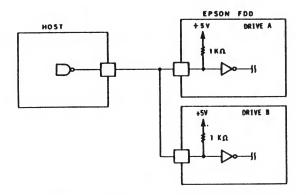

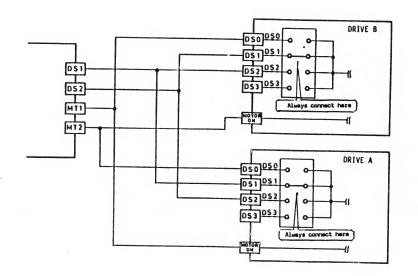

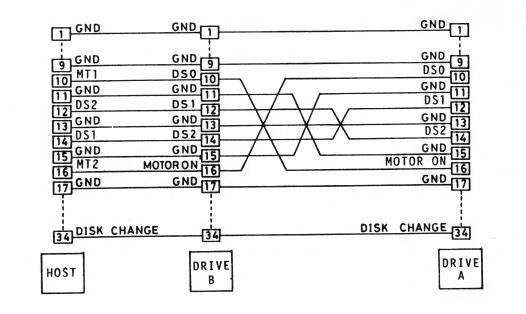

| 2-50<br>2-51     | FDD Terminator Function                                                                                                                       |

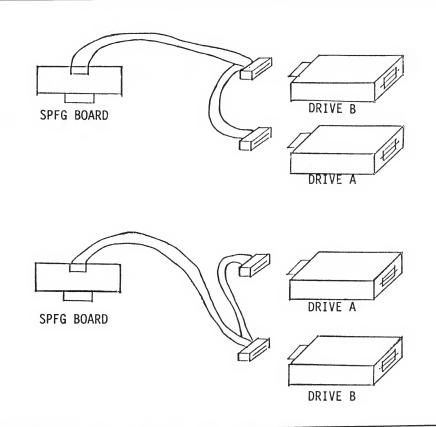

|                  | FDD Cable Connection                                                                                                                          |

| 2-52             | Drive Select and Motor on Signal Circuit                                                                                                      |

| 2 - 53<br>2 - 54 | FDD Special Signal Cable                                                                                                                      |

| 2-54<br>2-55     | Keyboard Unit Block Diagram                                                                                                                   |

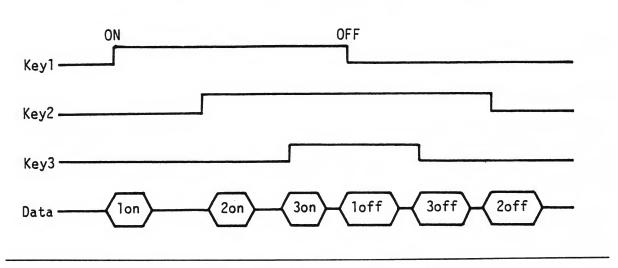

| 2 - 55<br>2 - 56 | Keyboard Data Output – AT mode                                                                                                                |

| 2 - 50           | Keyboard Data Input – AT mode                                                                                                                 |

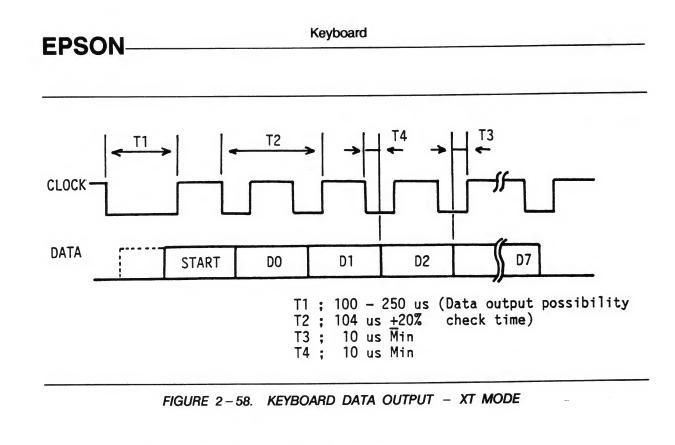

| 2-57             | Keyboard Data Output – XT mode                                                                                                                |

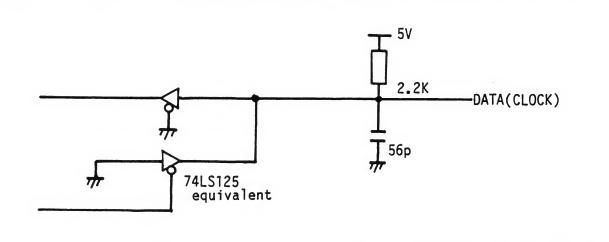

| 2 – 58<br>2 – 59 | Interface Circuit                                                                                                                             |

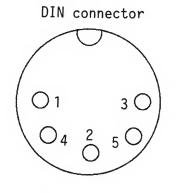

| 2 - 60           | Keyboard Connector Pin Locations                                                                                                              |

| 2-61             | Stroke Characteristics                                                                                                                        |

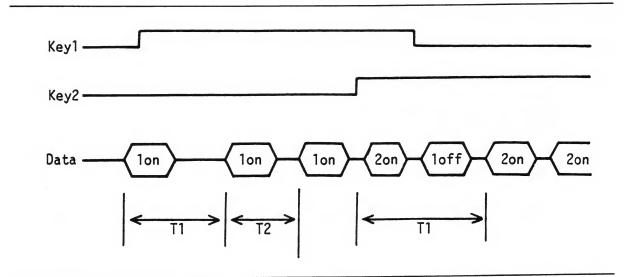

| 2-62             | Typematic Function                                                                                                                            |

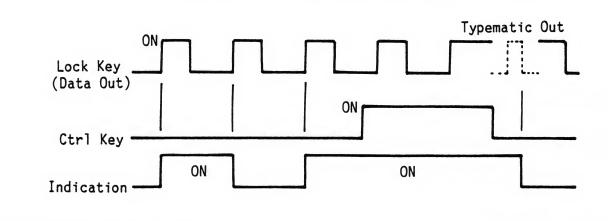

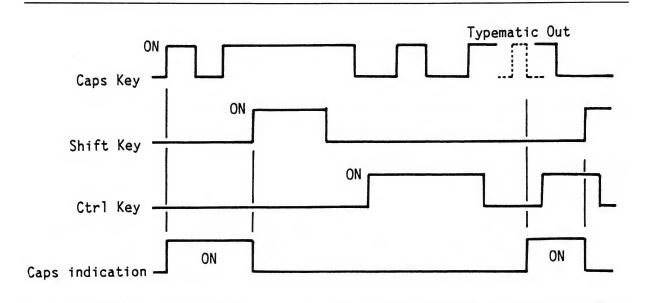

| 2-63             | Basic Operation of Mode Indicator Display                                                                                                     |

| 2-63<br>2-64     | Special Functions of Mode Indicator Display                                                                                                   |

| 2-65             | GAATAB Internal Block Diagram                                                                                                                 |

| 2 - 65<br>2 - 66 | GAATAB Internal Block Diagram                                                                                                                 |

| 2-60             | GAATOB Internal Block Diagram                                                                                                                 |

| 2-67             | GAATCK Internal Block Diagram – I                                                                                                             |

| 2 - 68<br>2 - 69 | GAATCK Internal Block Diagram – II                                                                                                            |

| 2 - 69<br>2 - 70 | GAATM2 Internal Block Diagram                                                                                                                 |

| 2-70             | GAATIO Internal Block Diagram – I                                                                                                             |

| 2-71<br>2-72     | GAATIO Internal Block Diagram – II                                                                                                            |

|                  | GAATIO Internal Block Diagram – III                                                                                                           |

| 2 - 73<br>2 - 74 | GAATHO Internal Block Diagram – I                                                                                                             |

| 2-74<br>2-75     | GAATM1 Internal Block Diagram – II                                                                                                            |

| 2-75             | GAATM1 Internal Block Diagram – III                                                                                                           |

| 2-76             | GAATRF Internal Block Diagram                                                                                                                 |

| 2-77             | GAATHE IIILEIIIdi DIUCK Diagiani                                                                                                              |

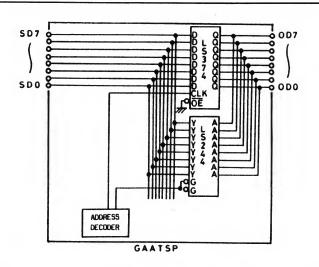

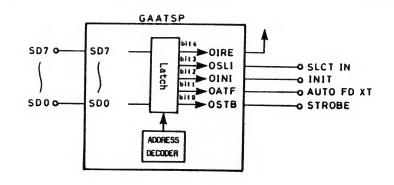

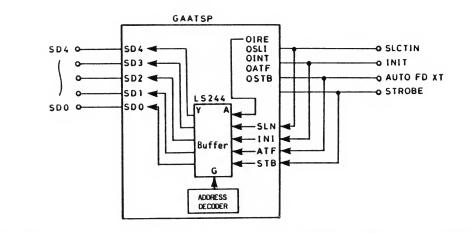

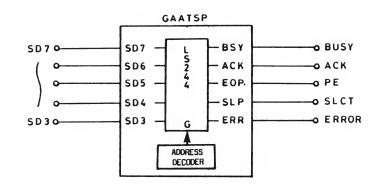

| 2 – 78 | GAATSP Internal Block Diagram – I  | - 129 |

|--------|------------------------------------|-------|

| 2 – 79 | GAATSP Internal Block Diagram - II | - 130 |

| 2 - 80 | GAATCX Internal Block Diagram      | - 132 |

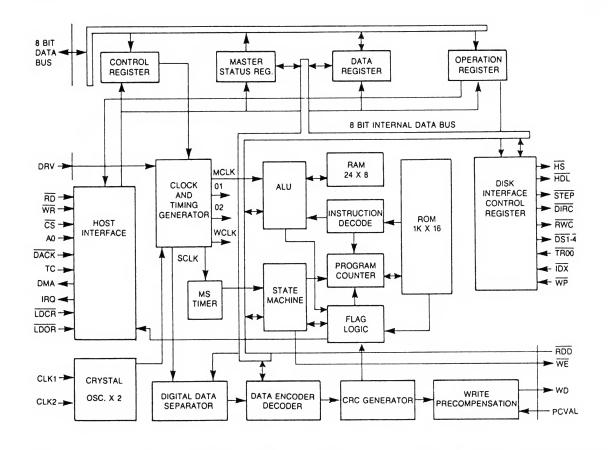

| 2 – 81 | WD37C65 Internal Block Diagram     | - 135 |

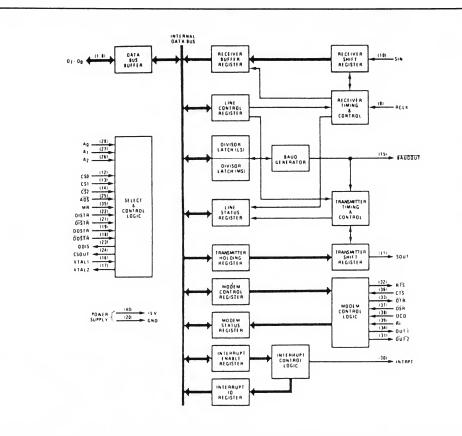

| 2 - 82 | NS16450 Internal Block Diagram     | - 138 |

| 2 - 83 | T4758 Internal Block Diagram       | - 140 |

## LIST OF TABLES

Tabla

Title

| lable  | inte                                                       | Page   |

|--------|------------------------------------------------------------|--------|

| 2-1    | DC Output Ranges                                           | 2-3    |

| 2-2    | Memory Map                                                 |        |

| 2-3    | LED Indications                                            | 2-15   |

| 2-4    | NPX Operation Speed                                        | 2 - 15 |

| 2-5    | Oscillator Clock Signal Flow                               | 2 - 16 |

| 2-6    | Reset Signal Generation Methods                            | 2-16   |

| 2-7    | Function of RAM Chips                                      |        |

| 2 – 8  | Jumper Connector Function                                  | 2 - 20 |

| 2-9    | CPU Data Access Mode Diagram List                          | 2 - 22 |

| 2 – 10 | Functions of Control Signal on GAATDB                      |        |

| 2 – 11 | Explanation of 74LS612                                     |        |

| 2-12   | Device Access Times and Wait Cycles                        | 2 - 40 |

| 2 – 13 | Wait Cycle Selection                                       |        |

| 2-14   | A20 Signal Control by GAATRF                               | 2 - 52 |

| 2 – 15 | Jumper J9 Setting                                          | 2 - 55 |

| 2 – 16 | Difference between 1.2MB FDD of SD-581L and FD1155C/MD5501 | 2-60   |

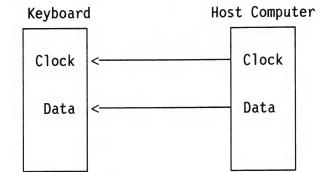

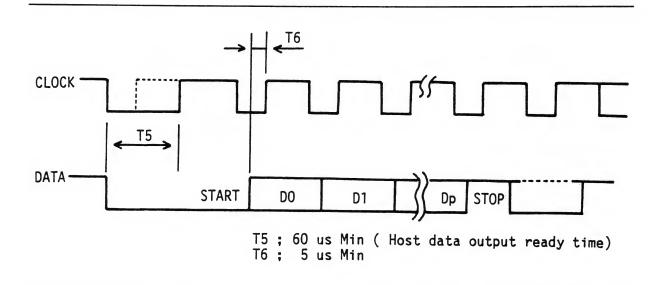

| 2 – 17 | Interface Control Mode                                     |        |

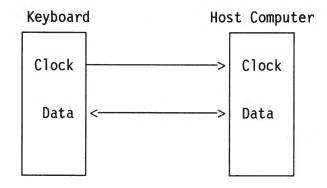

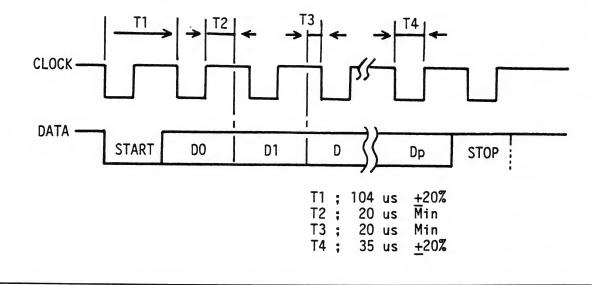

| 2 – 18 | Data Communication Mode (at AT Mode)                       | 2-66   |

| 2 – 19 | Data Communication Mode (at XT Mode)                       |        |

| 2-20   | Data Transmission Method and Data Format                   | 2-67   |

| 2 – 21 | Keyboard Connector Pin Function                            |        |

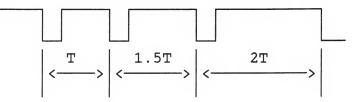

| 2 – 22 | Transmission Intervals                                     | 2-72   |

| 2 – 23 | Overrun Codes                                              |        |

| 2 – 24 | Key Code Make Up                                           |        |

| 2 – 25 | Condition for Setting and Releasing Numeric Lock           |        |

| 2 – 26 | Extension SHIFT Key - Stroke Conditions                    |        |

| 2 – 27 | Extension Left and Right SHIFT Codes                       |        |

| 2 – 28 | Transmission Sequence of Left and Right Codes Key          |        |

| 2 – 29 | Transmitted Code of F16 (BREAK) Key                        |        |

| 2 – 30 | Transmitted Code of F14 (Sys Rq) Key                       |        |

| 2 – 31 | Keyboard Commands (AT Mode)                                | 2 - 79 |

| 2 – 32 | Typematic Rate/Delay                                       | 2 - 80 |

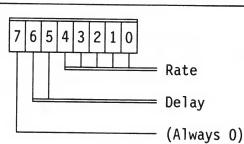

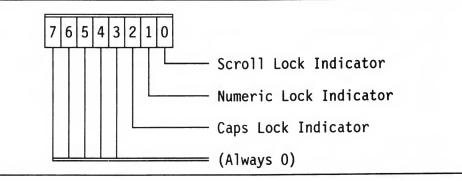

| 2 – 33 | Option Register for Keyboard                               | 2 – 81 |

| 2 – 34 | Key Code Mode Status                                       |        |

| 2 – 35 | Key Code Mode on Option Data                               |        |

| 2 – 36 | All Key Typematic Control                                  | 2 - 82 |

| 2 – 37 | Commands to the Host Side                                  |        |

| 2 – 38 | GAATAB Pin Description                                     |        |

| 2 – 39 | GAATCB Pin Description                                     |        |

| 2 – 40 | GAATDB Pin Description                                     |        |

Rev. A

| 2 - 41 | GAATCK Pin Description  |

|--------|-------------------------|

| 2 - 42 | GAATM2 Pin Description  |

| 2 - 43 | GAATIO Pin Description  |

| 2 – 44 | GAATM1 Pin Description  |

| 2 - 45 | GAATRF Pin Description  |

| 2 - 46 | GAATSP Pin Description  |

| 2 - 47 | GAATCX Pin Description  |

| 2 - 48 | WD37C65 Pin Description |

| 2 - 49 | NS16450 Pin Description |

.

# 2.1 SYSTEM OVERVIEW

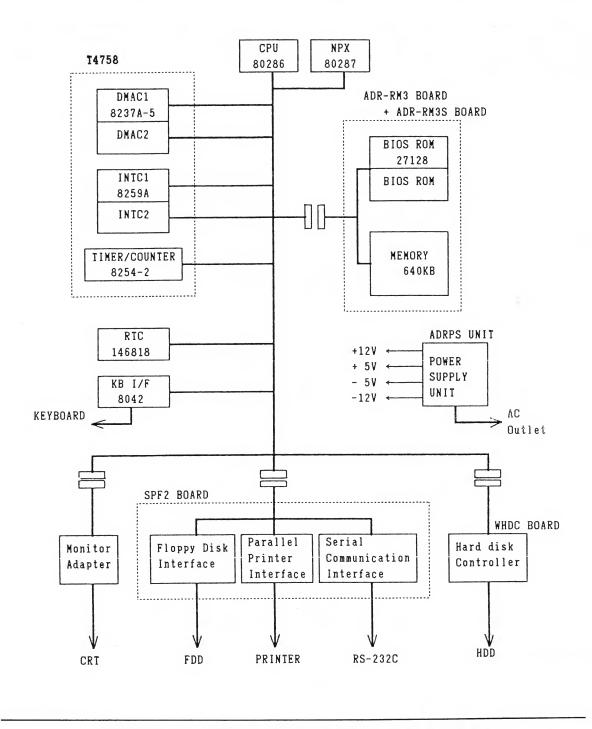

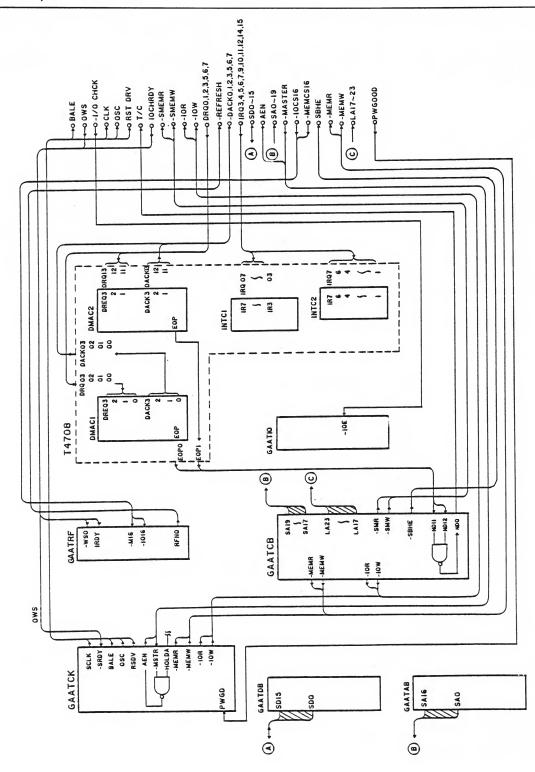

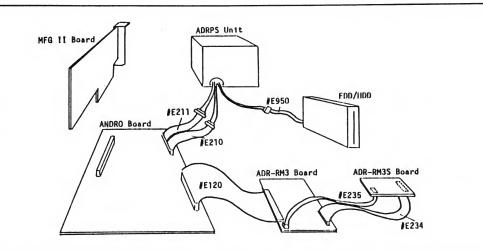

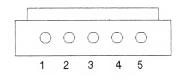

Figure 2 – 1 shows the interconnection of the main CPU unit, floppy disk drives, the keyboard, and the monitor. Pin assignments for each connector are detailed in Appendix.

FIGURE 2-1. SYSTEM CONFIGURATION BLOCK DIAGRAM

Page 2 - 1

# 2.2 ADRPS POWER SUPPLY UNIT

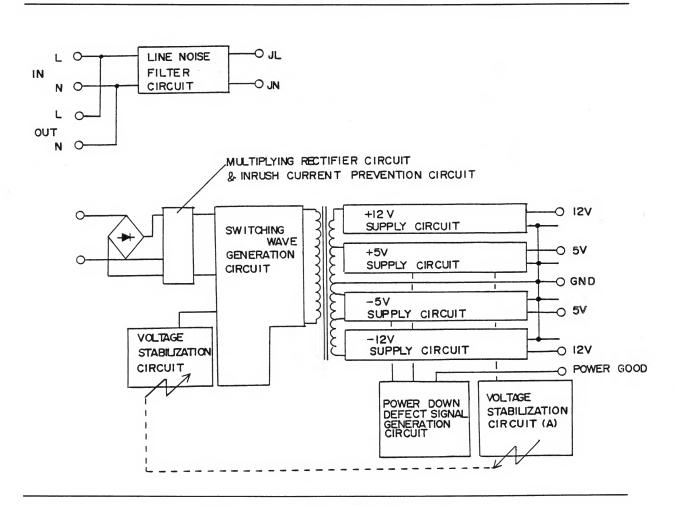

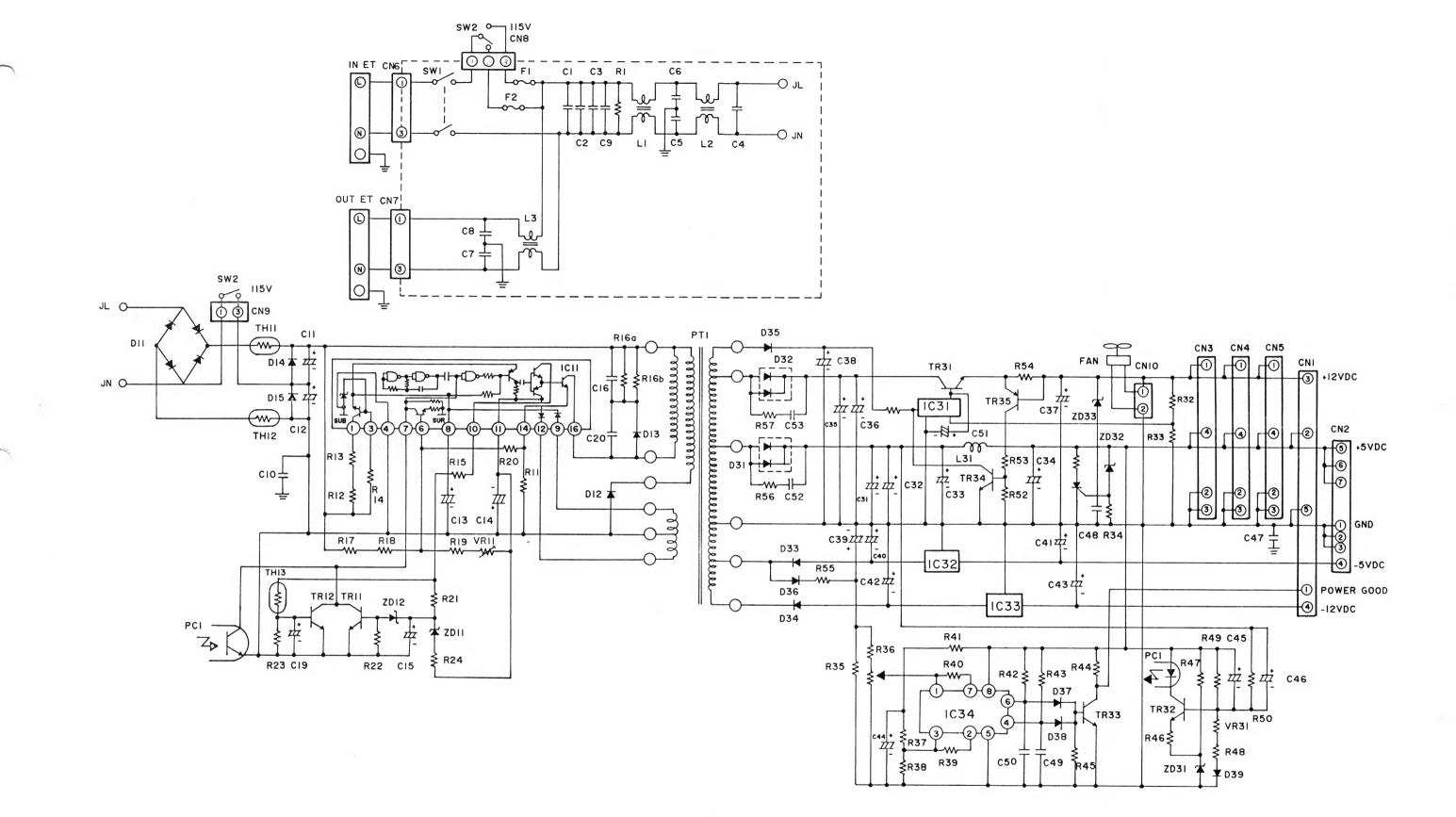

The EQUITY II + / EPSON PC AX2 power supply, simply called the ADRPS unit is a switching power supply of the ringing choke converter (RCC) type. It produces four DC voltages +5V, -5V, +12V, and -12V from the 115V or 230V input. The unit conforms to safety standards UL478, CSA C - 22, 2 - 154, and TUV; and noise standards FCC class B, and FTZ class B. It is housed in a light alloy case and positioned on the right at the rear of the main unit. The unit supplies power to the system board, adapter board, FDD, HDD, K/B, and monochromatic CRT.

The power supply has a voltage doubler rectification circuit that can switch the input voltage range to either 115 - 120V or 220 - 240V, 50/60Hz, so that it can be used anywhere in the world. The input voltage can be switched to either 115V AC or 230V AC by the two position slide switch on the rear panel.

FIGURE 2-2. POWER SUPPLY DIAGRAM

#### AC OUTPUT RATING

The unit has an AC output socket that supplies a maximum output current of 1A to an optional external device, such as a CRT.

#### DC OUTPUT RATING

Table 2-1 shows the DC output ratings.

| BASIS GROUND<br>OF VOLTAGE  | GL       | GP       | GL       | GL       |  |  |  |

|-----------------------------|----------|----------|----------|----------|--|--|--|

| RATED OUTPUT<br>VOLTAGE     | +5 V     | +12 V    | -12 V    | -5 V     |  |  |  |

| RATED OUTPUT<br>CURRENT     | 10 A     | 4.5 A    | 0.3 A    | 0.3 A    |  |  |  |

| MINIMUM OUTPUT<br>_ CURRENT | 1.0 A    | 0 A      | 0 A      | 0 A      |  |  |  |

| REGULATION                  | +-5%     | +-5%     | +-10%    | +-10%    |  |  |  |

| RIPPLE                      | 50 mVpp  | 100 mVpp | 100 mVpp | 50 mVpp  |  |  |  |

| RIPPLE + NOISE              | 100 mVpp | 200 mVpp | 200 mVpp | 100 mVpp |  |  |  |

| OVERCURRENT<br>PROTECTION   | YES      | YES      | YES      | YES      |  |  |  |

| OVERVOLTAGE<br>PROTECTION   | YES      | NO       | NO       | NO       |  |  |  |

TABLE 2-1. DC OUTPUT RATINGS

## 2.2.1 PRIMARY – SIDE CIRCUITS

#### 2.2.1.1 AC VOLTAGE INPUT SELECTION CIRCUIT

The user can select the AC input voltage by setting the two position slide switch (SW2) on the rear of the unit to either 115V or 230V. The unit supplies current to the circuit appropriate to the input voltage selected by SW2; the fuse, voltage doubler rectification circuit, and surge current prevention circuit for the 115V AC input are different from those for the 230V AC input. In a 110V AC system, current flows through fuse F1, and in a 230V AC system, it flows through fuse F2. (See figure 2-1) The voltage doubler rectification circuit and surge current prevention circuit are described below.

# EPSON-

#### 2.2.1.2 LINE - NOISE FILTER CIRCUIT

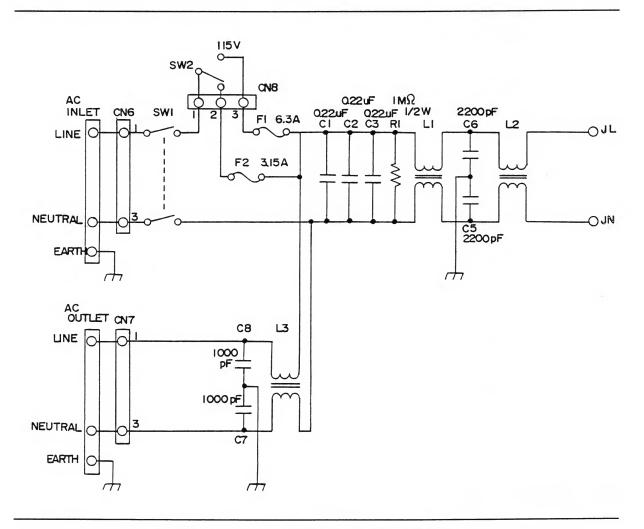

The line – noise filter circuit prevents malfunction due to input surge voltage or input return noise. C1, C2, C3, and R1 C4 remove normal – mode noise; L1, L2, C5, and C6 remove common – mode noise. Figure 2–1 shows the line – noise filter circuit.

FIGURE 2-3. LINE NOISE FILTER CIRCUIT

#### 2.2.1.3 VOLTAGE RECTIFICATION AND SURGE PREVENTION CIRCUIT

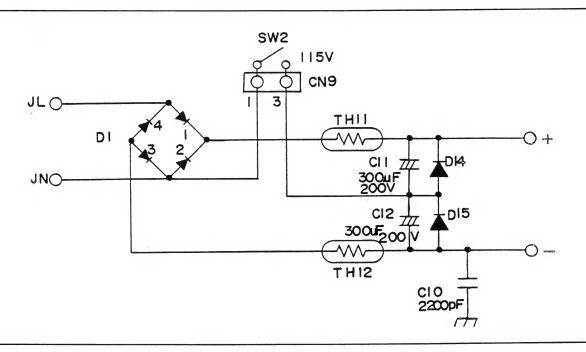

The voltage doubler rectification circuit and surge current prevention circuit differ according to the AC input voltage. The voltage doubler rectification circuit rectifies the 115V AC voltage to produce 230V AC. It consists of D1, C11, and C12. The surge current prevention circuit prevents a large current from flowing into the rectifying capacitor when power is turned on and protects components. This circuit contains TH11 and TH12. SW2 is closed when the input voltage is 115V AC. A positive half cycle input through the AC line conducts D1 - 1, buffers surge current by TH11, charges C11 to the maximum voltage, and flows to the neutral side through SW2. The negative half cycle that follows induces current from the neutral side. The current passing through SW2 charges C12 to the same voltage as C11 in the same direction, then

Page 2 - 4

# EPSON-

flows to the line through TH12. Thus, a DC current with twice the AC input voltage is obtained for the system. SW2 is open when the AC input voltage is 230V AC, and therefore, normal bridge rectification is performed. Figure 2-2 shows the voltage doubler rectification circuit and surge current prevention circuit.

Figure 2-4. VOLTAGE DOUBLER RECTIFIER CIRCUIT

#### 2.2.1.4 SWITCHING - WAVE GENERATION CIRCUIT

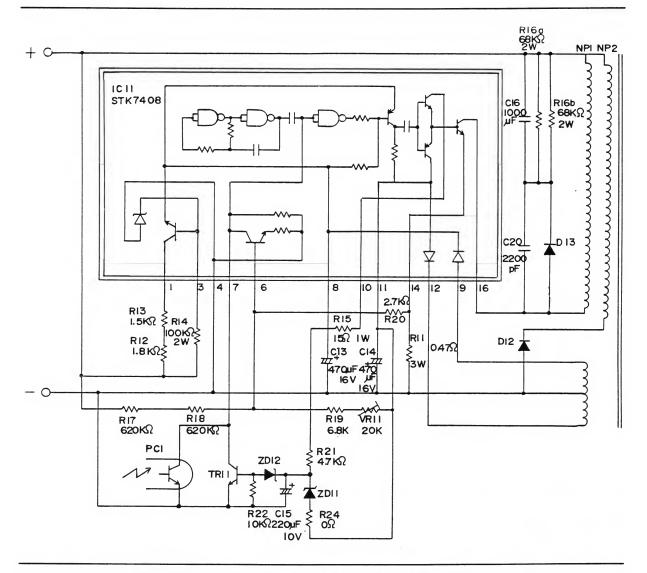

The offline switching IC, IC11 (STK7408), generates switching pulses with a frequency of 33KHz and drives the primary side of the pulse transformer PT1. The PT1 primary winding NP1 is used to drive the secondary side, and Np2 returns excess current from the secondary side load to the primary side. D13, C16, R16a and R16b form a snubber circuit that buffers the spike voltage that occurs on switching off. The circuit consisting of ZD11, ZD12, and TR11 is the soft start overshooting. Figure 2-3 shows the switching wave generation circuit.

FIGURE 2-5. SWITCHING WAVE GENERATION CIRCUIT

## 2.2.2 SECONDARY - SIDE CIRCUIT

#### 2.2.2.1 + 12V SUPPLY CIRCUIT

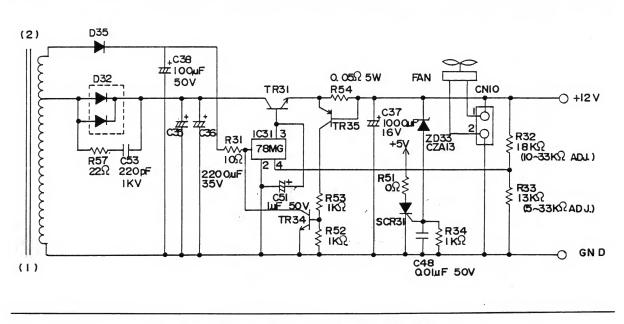

When the primary side switching is OFF, an electro-motive force (EMF) is produced in PT1 in the direction of (1), and the current is rectified by D32 and supplied by charging C35 and C36.

When the primary side switching is On, an EMF is generated in PT1 in the direction of (2) and the current is supplied by discharging C35 and C36. C57 and C53 prevent the spike voltage.

This circuit is a dropper-type stabilizing power supply containing voltage regulator IC3 (78MG) and TR31. R54 and TR35 detect overcurrent, turn TR34 on, and decrease the TR31 collector current by controlling IC31 input. ZD33 forms a clover overvoltage protection circuit by

connecting the anode to the SCR31 gate. R32 and R33 detect the reference voltage and stabilize the voltage by controlling IC31. Figure 2-6 shows the +12V supply circuit.

FIGURE 2-6. +12V SUPPLY CIRCUIT

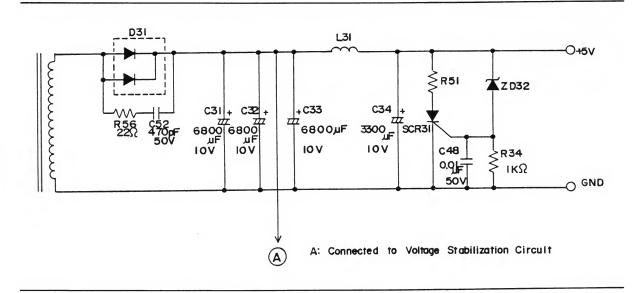

## 2.2.2.2 +5V SUPPLY CIRCUIT

The basic operations of the +5V supply circuit are the same as those of the +12V DC supply circuit described above. L31 removes ripples; ZD32 and SCR31 form a clover overvoltage protection circuit. Figure 2-7 shows the +5V supply circuit.

Figure 2-7. +5V SUPPLY CIRCUIT

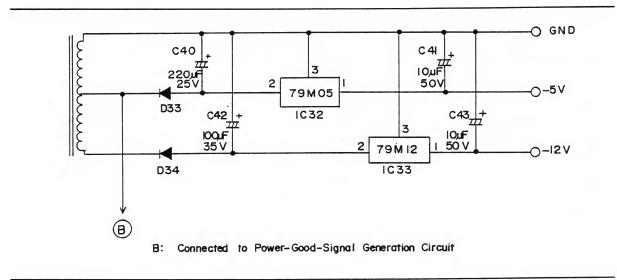

## 2.2.2.3 - 5V / - 12V SUPPLY CIRCUIT

The basic operations of the -5V / -12V supply circuit are the same as those of the +12V supply circuit. -5V DC is generated and supplied by IC32 (79M05). -12V DC is generated and supplied by IC33 (79M12). Figure 2-8 shows the -5V / -12V supply circuit.

## FIGURE 2-8. -5V / -12V SUPPLY CIRCUIT

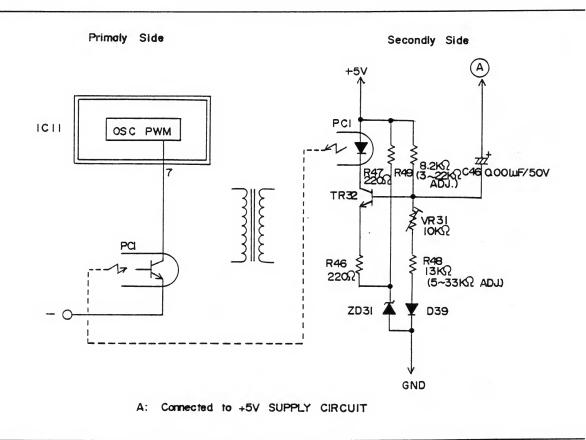

## 2.2.2.4 OUTPUT - VOLTAGE STABILIZATION CIRCUIT

The output – voltage stabilization circuit stabilizes the secondary side output voltage by detecting a variation in the +5V voltage and controlling the primary side generation. The reference voltage is detected by the ZD31 cathode. When the voltage is higher than the reference voltage, ZD31 passes current from the cathode to the anode, turns on the PC1 photodiode, and so sends a signal to the primary side. The PC1 phototransistor which receives the signal reduces the time constant of the generation circuit in the switching regulator power IC (IC11) by increasing the collector current. This phototransistor decreases the secondary side output voltage by reducing the switching duty. When the voltage is lower than the reference voltage, the reverse of the above operations is performed. The output voltage is stabilized by these operations being repeatedly performed. Figure 2–9 shows the circuit.

FIGURE 2-9. OUTPUT VOLTAGE STABILIZATION CIRCUIT

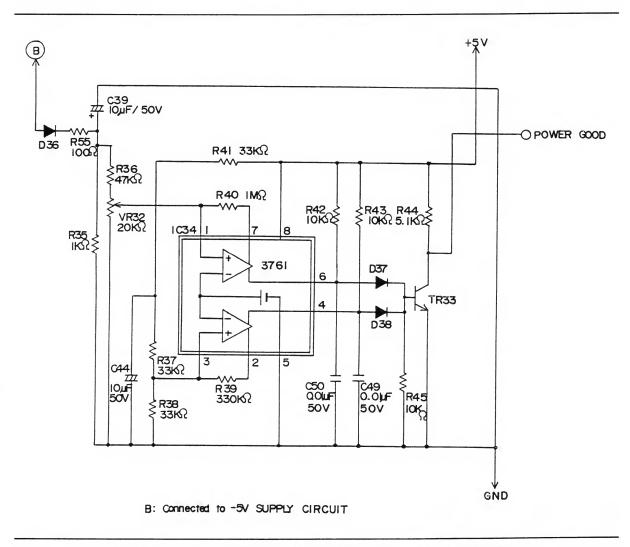

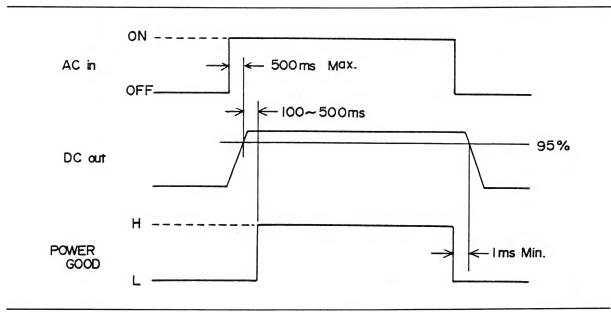

## 2.2.2.5 POWER DOWN CIRCUIT

When the supply voltage drops to the extent that the machine cannot be operated normally, the voltage drop is reported to the main system unit. The POWER DOWN signal is output just before the supply voltage drops due to a power failure or interruption, and sends a top – priority inter – rupt to the CPU. The voltage detection comparator IC34 (3761) indirectly monitors the input voltage making use of the fact that the output from the +5V transformer is proportional to the primary side input voltage. This comparator also monitors the output voltage of the +5V line. When a drop in one of the voltages is detected, IC34 turns TR33 on and forces the POWER DOWN signal low. Figure 2–10 shows the POWER DOWN circuit.

FIGURE 2-10. POWER DOWN SIGNAL GENERATION CIRCUIT

FIGURE 2-11. POWER DOWN TIMING CHART

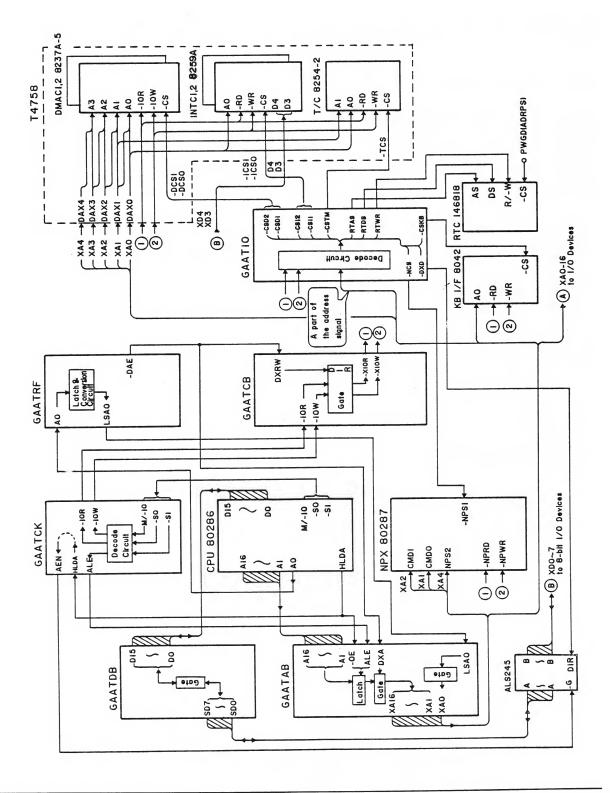

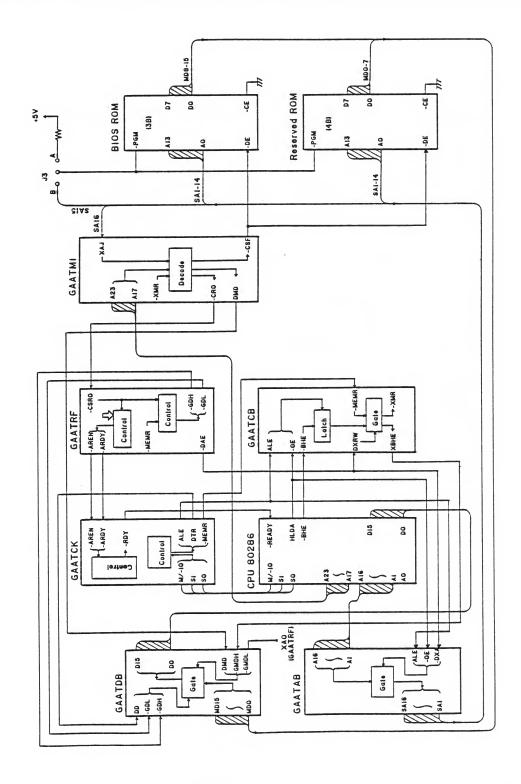

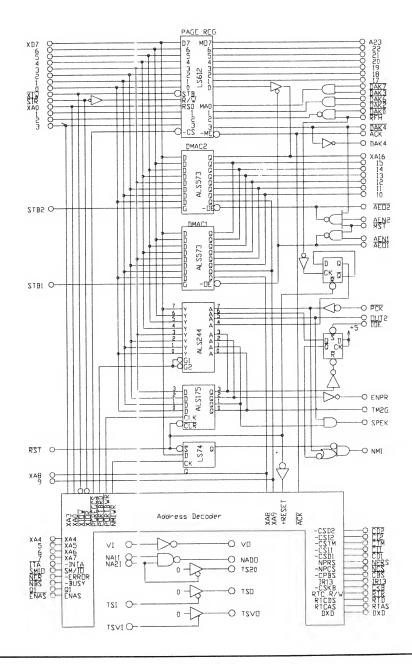

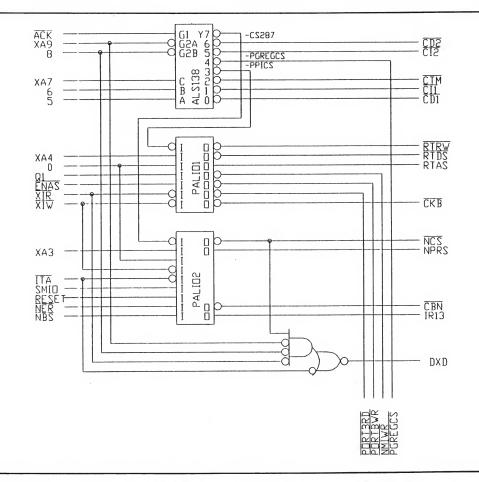

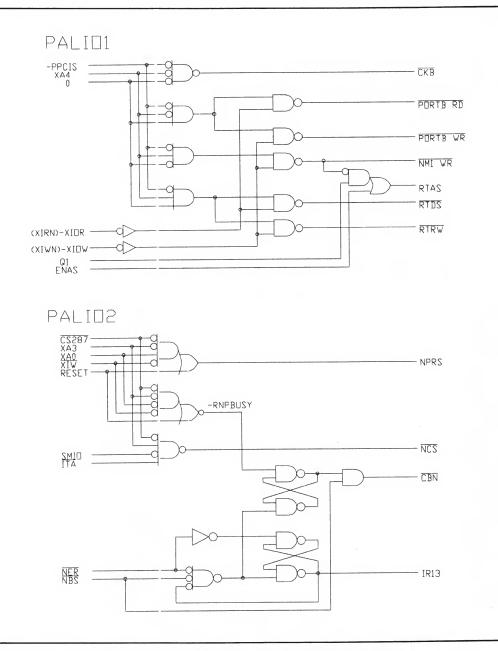

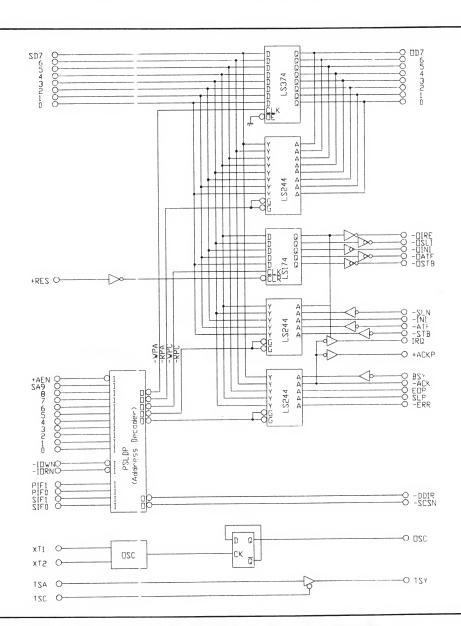

# **2.3 ANDRO Board Main Control Operations**

This section describes the important internal circuits of the EQUITY II + / EPSON PC AX2 system board. The diagram on the next page shows the relative positions of the custom gate array chips on the system board (ANDRO) and the memory board (ADR - RM3 / ADR - RM3S).

The table below shows the memory map for the EQUITY II + / EPSON PC AX2 computer system.

| ADDRESS                                                                                | NAME                                                                                   | FUNCTION                                                                                                                           |

|----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| 000000 to 09FFFF<br>0A0000 to 0BFFFF<br>0C0000 to 0DFFFF<br>0E0000 to 0EFFFF<br>FE0000 | 640 KB system memory<br>128 KB video RAM<br>128 KB I/O Expansion ROM<br>64 KB reserved | System memory<br>Reserved for graphics display buffer<br>Reserved for ROM on I/O adapters<br>Duplicated code assignment at address |

| 0F0000 to 0FFFFF<br>FF0000                                                             | 64 KB system board ROM                                                                 | Duplicated code assignment at address                                                                                              |

| 100000 to FDFFFF<br>FE0000 to FEFFFF<br>0E0000                                         | Extended/Expansion RAM<br>64 KB reserved                                               | I/O channel RAM – memory expansion option<br>Duplicated code assignment at address                                                 |

| FF0000 to FFFFFF<br>0F0000                                                             | 64 KB system board ROM                                                                 | Duplicated code assignment at address                                                                                              |

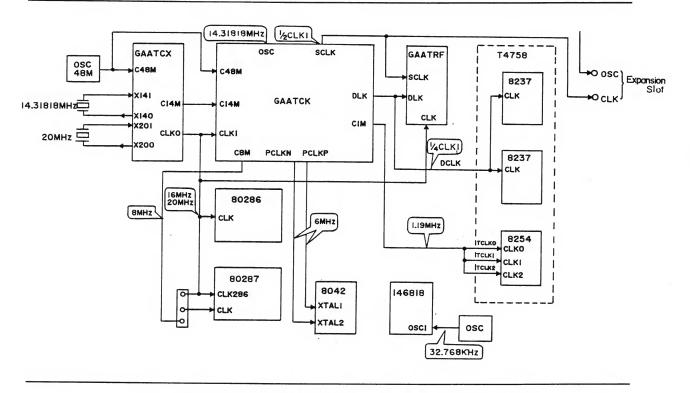

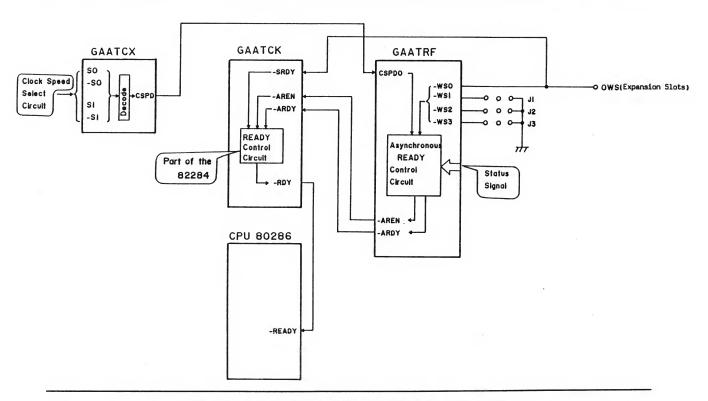

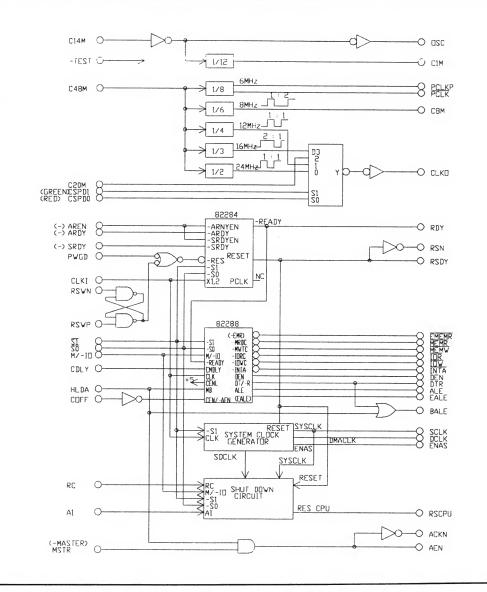

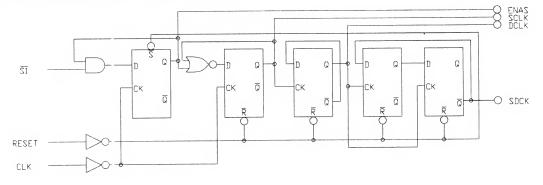

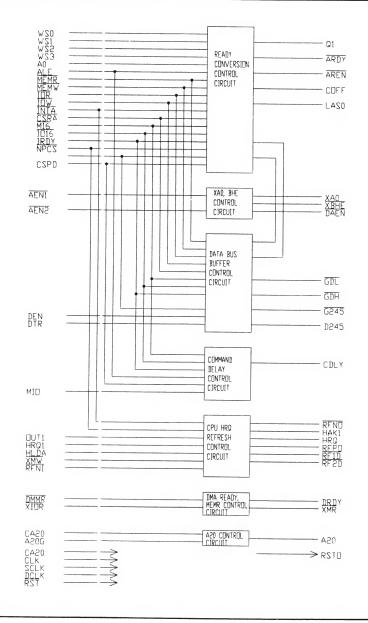

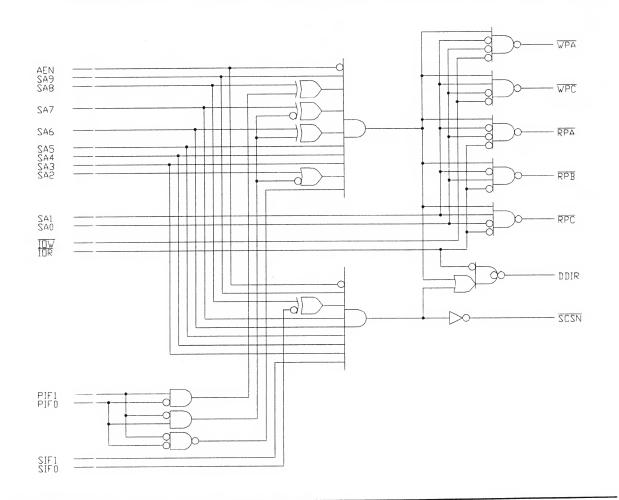

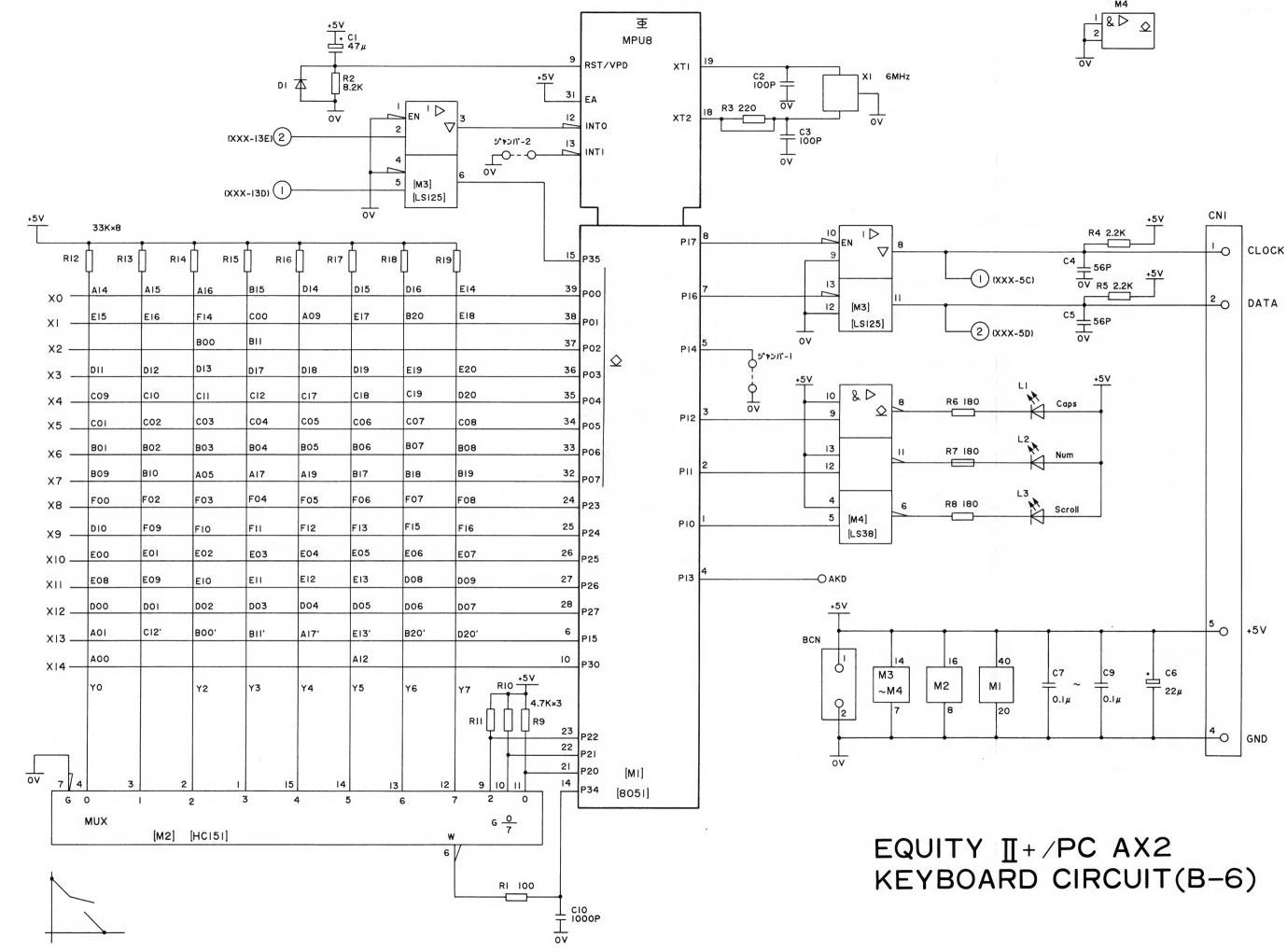

## 2.3.1 SYSTEM CLOCK GENERATION CIRCUIT

All clock signals are supplied by gate arrays GAATCK and GAATCX except the real-time clock (RTC) clock signal. GAATCK and GAATCX generate the following clock signals.

- 1) System clock (16MHz, 20MHz)

- 2) NPX clock (8MHz)

- 3) DMA clock (4MHz, 5MHz)

- 4) Timer/counter clock (1.19MHz)

- 5) Keyboard controller clock (6MHz)

- 6) OSC clock (for expansion slots: 14.31818MHz)

- 7) SCLK signal (System clock for expansion slots: 8MHz, 10MHz)

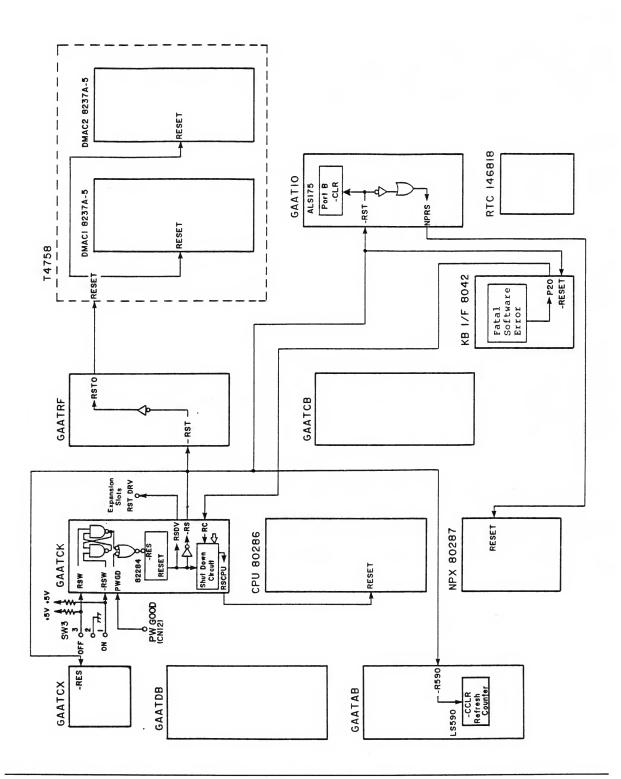

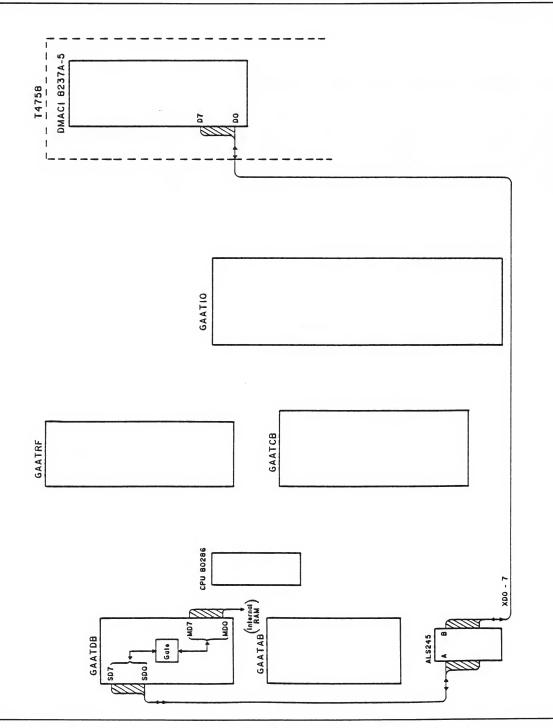

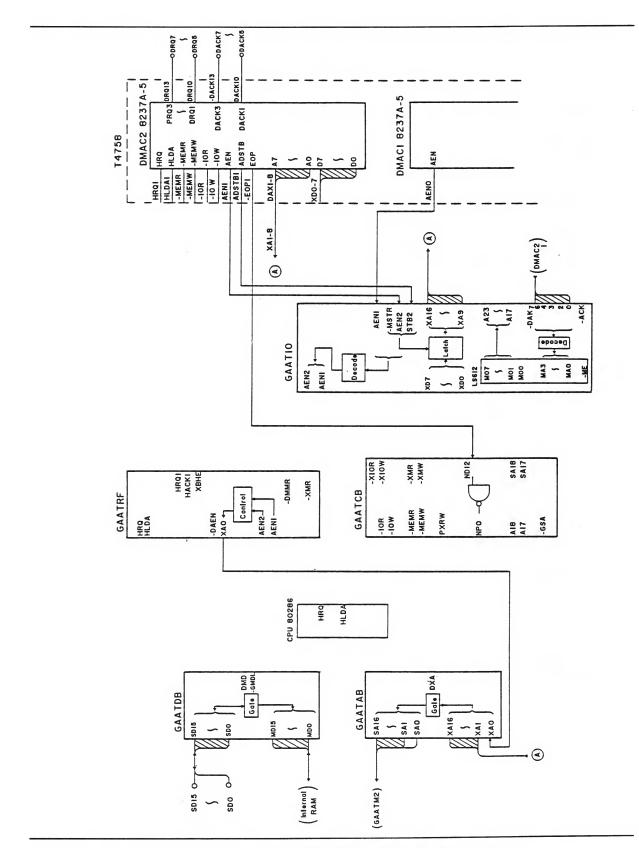

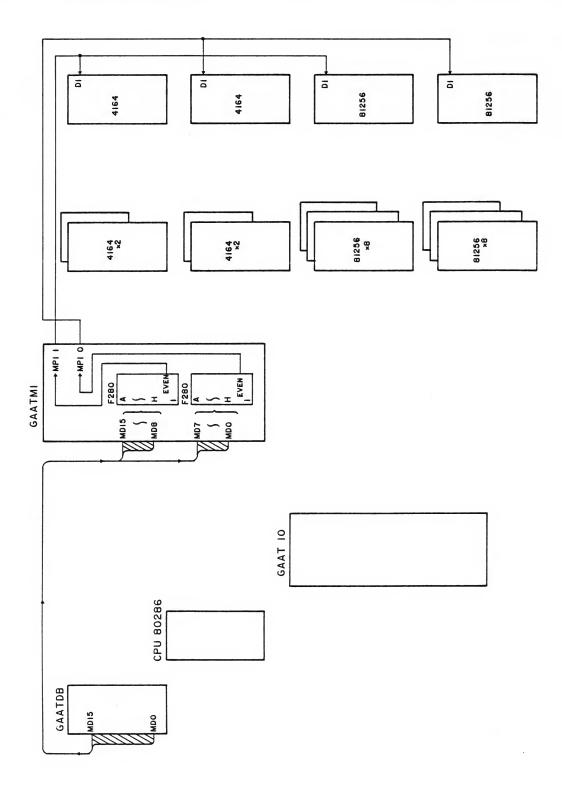

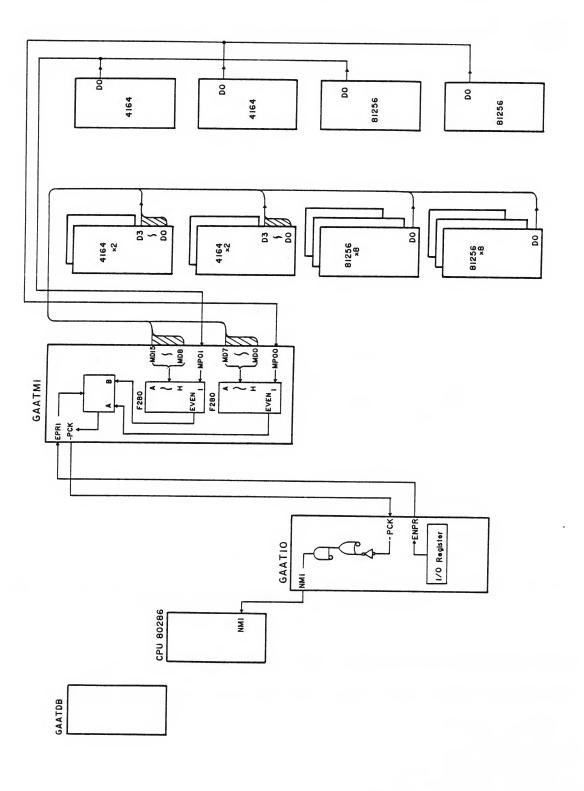

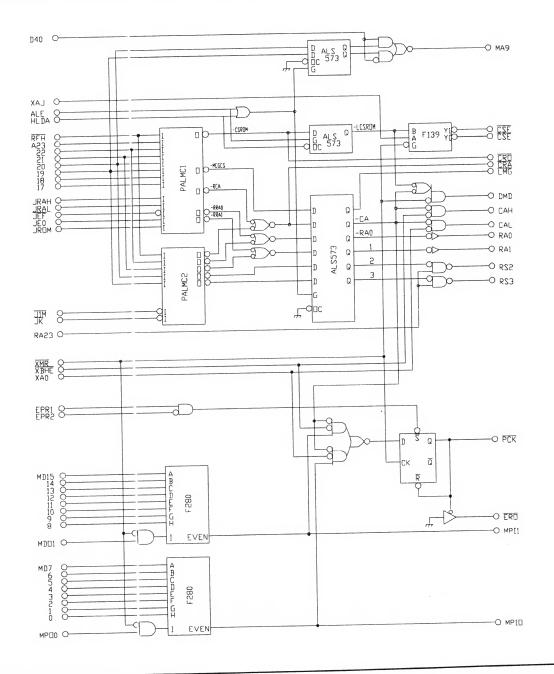

FIGURE 2-12. INTERNAL CIRCUIT CONFIGURATION

System Board

# EPSON-

FIGURE 2-13. SYSTEM CLOCK GENERATION CIRCUIT

NOTE:Please note the difference between the terms system clock and CPU clock. The 80286 (CPU) divides the system clock by two to obtain its operating clock signal. This manual defines these words as follows:

> System Clock: Internal "crystal" system clock (20MHz or 16MHz) CPU Clock: The operation speed of the CPU (System Clock/2)

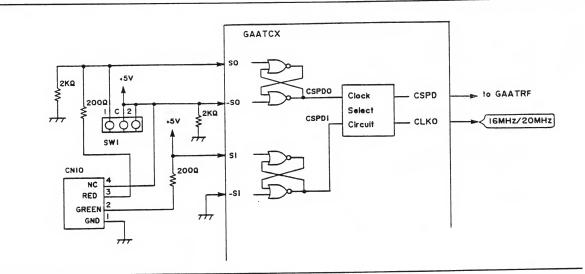

## 2.3.1.1 CLOCK SPEED SELECTION

The EQUITY II + / EPSON PC AX2 has two hardware – selectable CPU clock speeds: 8MHz and 10MHz. CPU clock speed is selected by the position of the slide switch (SW2) on the front panel of the main unit. The gate array GAATCX provides clock speed selection circuitry.

FIGURE 2-14. CLOCK SPEED SELECTION

## 2.3.1.2 LED INDICATORS

The power – on LED indicator on the front panel is connected to the clock speed change circuitry. Its color indicates the current CPU clock speed as shown below:

## TABLE 2-3. LED INDICATIONS

| LED INDICATION | CPU OPERATION SPEED |

|----------------|---------------------|

| ORANGE         | 8MHz                |

| GREEN          | 10MHz               |

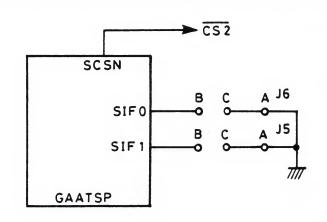

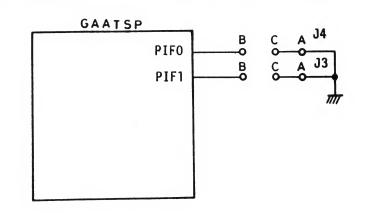

## 2.3.1.3 NPX (80287) CLOCK SPEED SELECTION

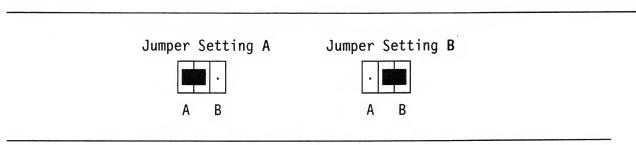

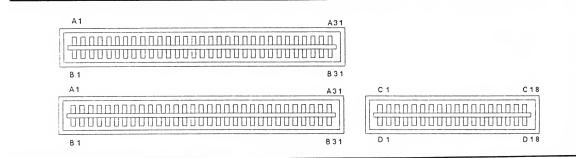

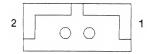

The EQUITY II + / EPSON PC AX2 has two NPX operation speed modes. The first mode, selected by setting system board jumpers J4 and J5 to "A", sets the NPX clock speed to 8MHz regardless of the CPU clock speed. The second mode, selected by setting jumpers J4 and J5 to "B", sets the NPX clock speed to be 2/3 of the CPU clock speed. The table below shows the resulting NPX clock speeds for each mode.

| MODE                   | CPU CLOCK | NPX CLOCK |

|------------------------|-----------|-----------|

| 8MHz Mode:             | 8MHz      | 8MHz      |

| (J4 and J5 set to "A") | 10MHz     | 8MHz      |

| 2/3 CPU Mode:          | 8MHz      | 5.33MHz   |

| (J4 and J5 set to "B") | 10MHz     | 6.66MHz   |

TABLE 2-4. NPX OPERATION SPEED

#### 2.3.1.4 OSCILLATORS

There are three oscillators on the ANDRO board: 48MHz, 20MHz and 14.31818MHz. The gate arrays GAATCX and GAATCK receive the timing signals from these oscillators and generate the timing signals shown in the table below.

| OSC Clock<br>Signal | GAATCX<br>Conversion | GAATCX<br>Generates | GAATCK<br>Conversion | GAATCK<br>Generates | Connected To        |

|---------------------|----------------------|---------------------|----------------------|---------------------|---------------------|

| 48MHz               | 1/3                  | 16MHz               | -                    |                     | CPU                 |

|                     | 1/3                  | 16MHz               | 1/2                  | 8MHz                | Expansion Slots     |

|                     | 1/3                  | 16MHz               | 1/4                  | 4MHz                | DMA Controller      |

|                     | -                    | _                   | 1/6                  | 8MHz                | NPX                 |

|                     | _                    | -                   | 1/8                  | 6MHz                | Keyboard Controller |

| 20MHz               | 1/1                  | 20MHz               | -                    | _                   | CPU                 |

|                     | 1/1                  | 20MHz               | 1/2                  | 10MHz               | Expansion Slots     |

|                     | 1/1                  | 20MHz               | 1/4                  | 5MHz                | DMA Controller      |

| 14.31818MH          | z 1/1                | 14.31818MH          | z 1/1                | 14.31818            | Expansion Slots     |

|                     | 1/1                  | 14.31818MH          | ,                    | 1.19MHz             | Timer/Counter       |

TABLE 2-5. OSCILLATOR CLOCK SIGNAL FLOW

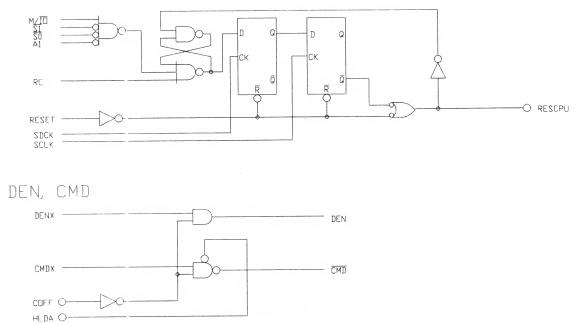

## 2.3.2 SYSTEM RESET SIGNAL GENERATION

There are three reset signals used in the EQUITY II + / EPSON PC AX2 computer system.

- 1) CPU Reset Signal

- 2) Internal Circuit Reset Signal

- 3) Expansion Slot Reset Signal

The gate array GAATCK generates these signals under the following conditions:

| RESET SIGNAL                  | CAUSE                                                                                                                       |  |

|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------|--|

| CPU Reset Signal              | PWGD signal goes low.<br>Reset switch is pushed.<br>RC signal goes active. (Software reset)<br>Shut down cycle is executed. |  |

| Internal Circuit Reset Signal | Reset switch is pushed.                                                                                                     |  |

| Expansion Slot Reset Signal   | Reset switch is pushed.                                                                                                     |  |

TABLE 2-6. RESET SIGNAL GENERATION METHODS

NOTE: The Software Reset command (RC goes active) resets only the CPU. When gate array GAATCK receives the RC signal, it generates the RSCPU signal.

FIGURE 2-15. SYSTEM RESET SIGNAL CIRCUIT

## 2.3.2.1 SYSTEM RESET CIRCUITS

#### PWGD signal

The power supply unit (ADRPS unit) generates the PWGD (power good) signal. Normally, this signal remains high. If the power supply is unable to supply current within the specified limits, the power supply unit will drive the PWGD signal LOW. A LOW PWGD signal will, in turn, cause GAATCK to activate all three system reset signals (-RS, RSDV, and RSCPU).

#### Reset switch (SW3)

When the reset switch SW3 is pushed, the GAATCK drives the three system reset signals (-RS, RSDV, and RSCPU) active.

#### RC signal

The RC signal can be sent, under software control, to GAATCK from P20 pin of the keyboard controller (8042). An active RC signal will cause GAATCK to reset the CPU by generating an RSCPU signal.

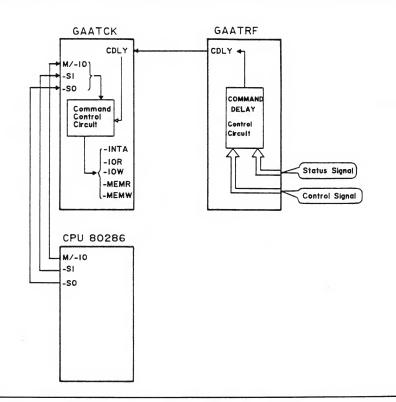

#### Shut down cycle

The Shutdown cycle is one of the 80286's execution cycles. The CPU executes this cycle when it detects a fatal software error and cannot continue the current operation. The CPU indicates this cycle through a combination of the - S0, - S1, and M/-IO signals. If GAATCK detects the CPU Shutdown cycle it generates an active RSCPU signal and resets the CPU.

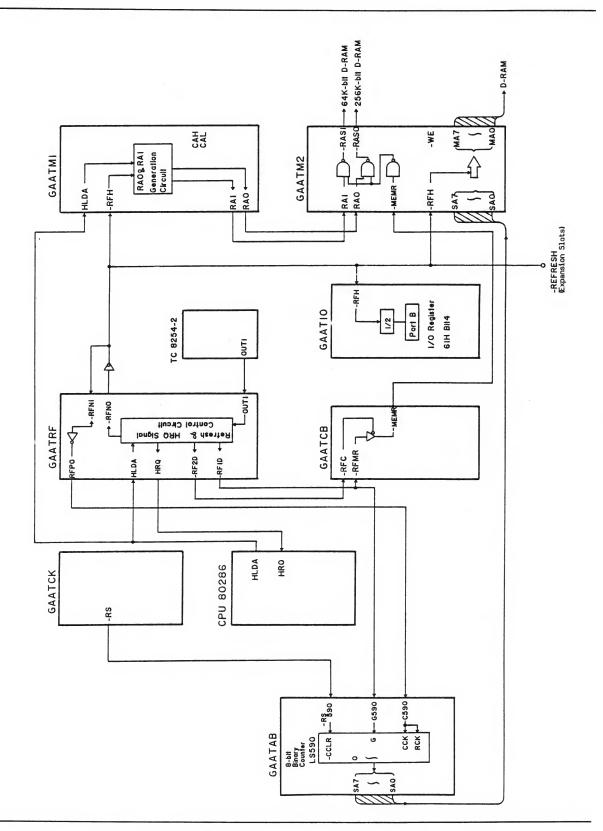

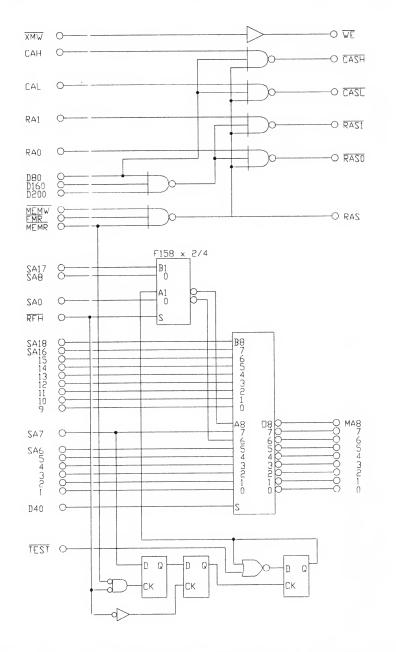

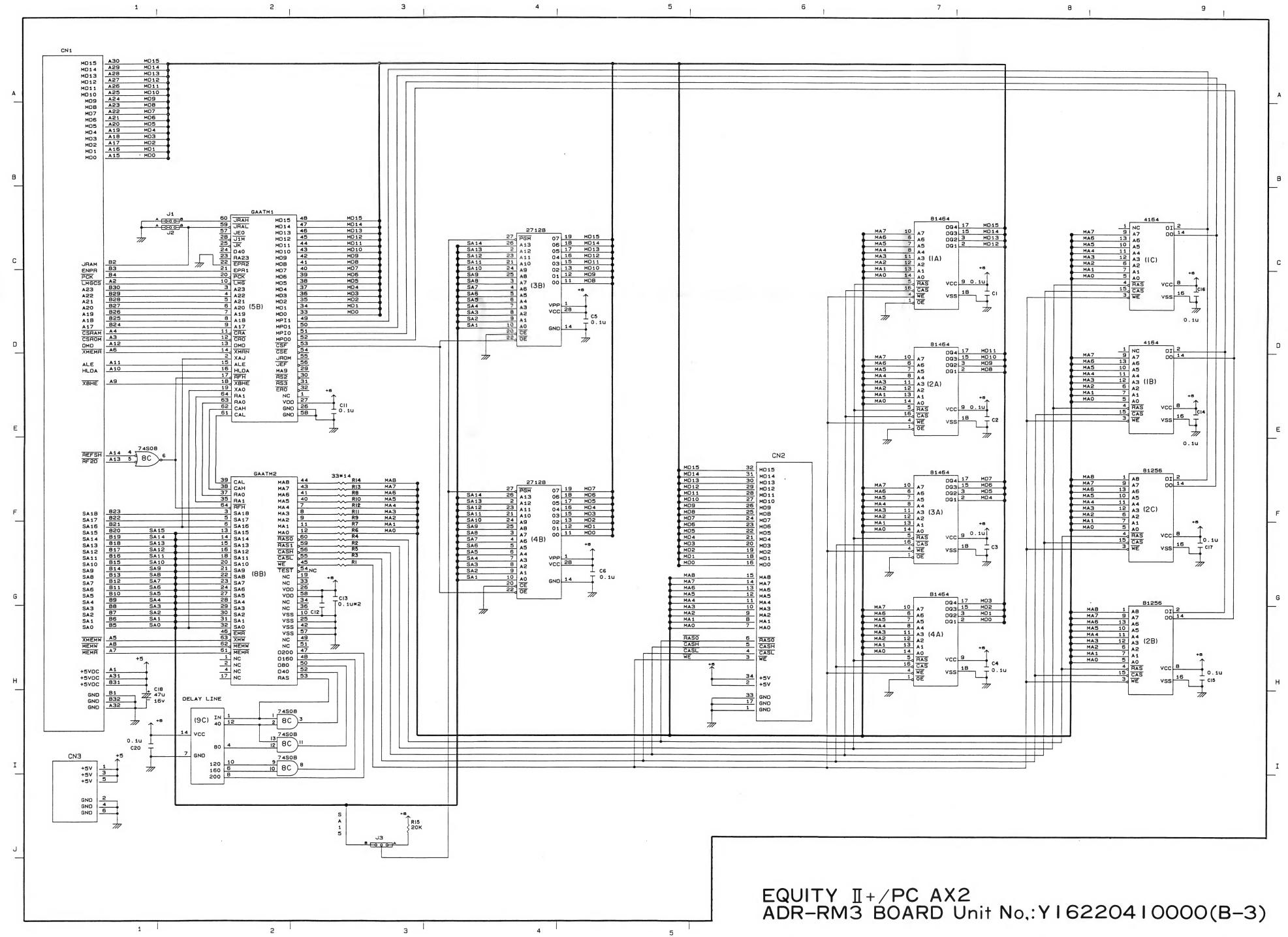

## 2.3.3 INTERNAL MEMORY CONTROL CIRCUIT

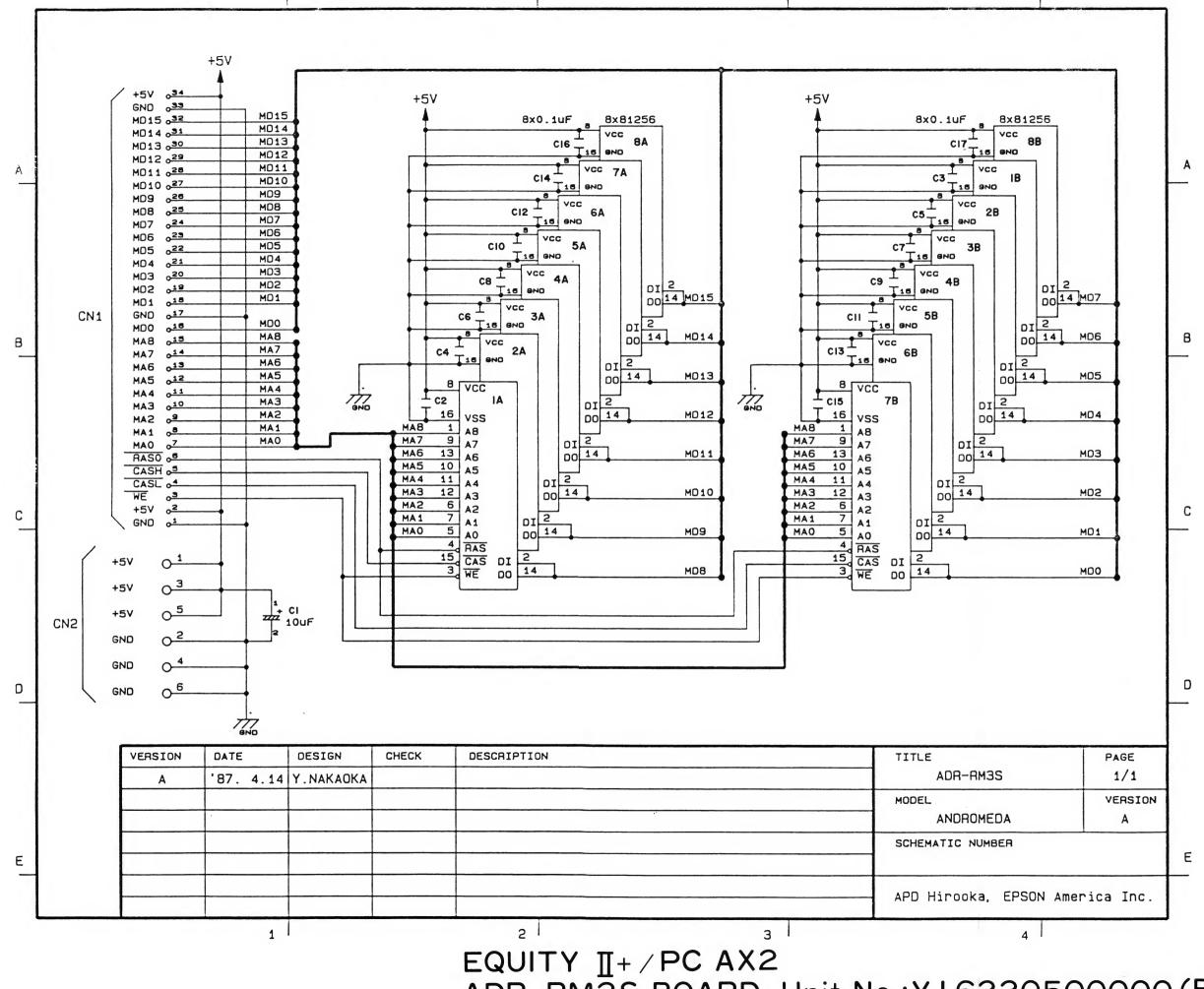

All system memory chips are located on the ADR – RM3 / ADR – RM3S board. If the system will not boot up it is recommended that the ADR – RM3 / ADR – RM3S board should be replaced first in order to determine whether the problem is caused by faulty RAM chips, or by a fault in another circuit.

System Board

FIGURE 2-16. INTERNAL MEMORY CONTROL CIRCUIT

## 2.3.3.1 RAM CHIP TYPE

There are two kinds of RAM chips on the ADR-RM3 / ADR-RM3S board.

| RAM CHIP TYPE     | Q'TY | FUNCTION              |

|-------------------|------|-----------------------|

| 256K-word by 1bit | 16   | System memory (512KB) |

| 64K-word by 4bit  | 4    | System memory (128KB) |

| 256K-word by 1bit | 2    | Parity check          |

| 64K-word by 1bit  | 2    | Parity check          |

TABLE 2-7. FUNCTION OF RAM CHIPS

#### 2.3.3.2. RAM CHIP ADDRESSES

The system memory RAM chips are located in the following addresses.

09FFFF -----

64K-word by 4bit RAM chips

080000

07FFFF

256K-word by 1bit RAM chips

000000

FIGURE 2-17. RAM CHIP ADDRESSES OF SYSTEM MEMORY

#### 2.3.3.3 SYSTEM MEMORY JUMPERS

It is possible to disable some of the system memory by setting jumper connectors J1 and J2 on the ADR – RM3 / ADR – RM3S board.

TABLE 2-8. JUMPER CONNECTOR FUNCTION

|   | mper<br>J1 | Functional Description                                   |  |  |

|---|------------|----------------------------------------------------------|--|--|

| A |            | 640K Bytes of RAM Enabled: 09FFFF - 000000               |  |  |

|   | B<br>A     | 512K Bytes of RAM Enabled: 07FFFF – 000000<br>(Not used) |  |  |

| В | В          | 256K Bytes of RAM Enabled: 03FFFF - 000000               |  |  |

## 2.3.3.4 MEMORY CONTROL CIRCUIT OPERATION

#### Address signals

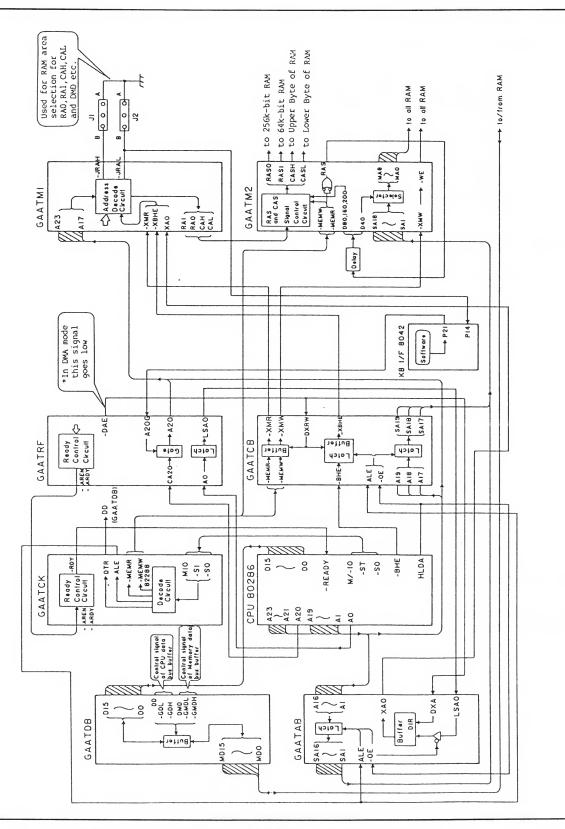

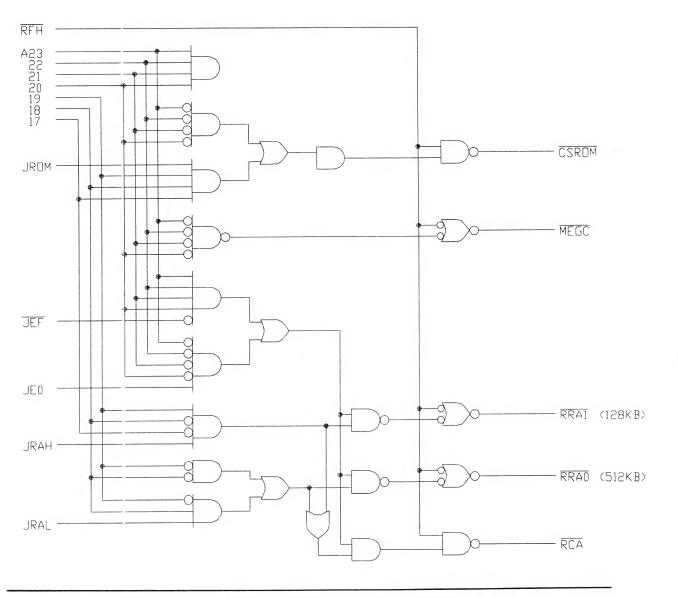

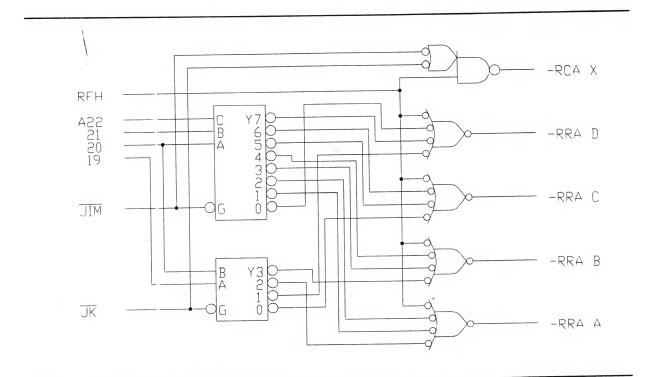

The address signal (on address bus lines A0 to A23) is generated by the CPU. GAATM2 (Memory control gate array 2) receives address signals A1 to A18 for the RAM chip address signals. GAATM1 (Memory control gate array 1) receives signals A0 and A17 – A23 and then generates the RAS, CAS and other memory address selection signals.

GAATRF, in combination with the 8042, controls the A20 signal from the CPU to insure correct performance of the A20 signal throughout the bus. Circuitry in the 8042 and GAATRF insure that the value of A20 will be 0 when the CPU is in REAL mode. Refer to section 2.3.14.6 for a logic table regarding A20 control.

The SA0 signal from gate array GAATAB is used during RAM refresh cycles, but is not used by the memory control circuit during RAM reads or writes.

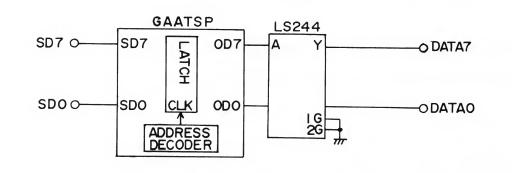

#### Data bus signals

Gate array GAATDB controls the memory data bus through its internal data bus buffer.

#### Read/Write control signals

The CPU bus cycle – type outputs – S0, – S1, and M/–IO, are received by gate array GAATCK. GAATCK, in turn, generates – MEMR and – MEMW signals which are used by GAATM2 to generate RAS and CAS signals. During a Write cycle GAATM2 receives the – XMW (– MEMW) signal from GAATCB, and generates the WE (Write Enable) signal for the RAM chips. During a Read cycle GAATM1 receives the – XMR (– MEMR) signal from GAATCB, and generates the RAS and CAS signals.

#### DRAM refresh control circuit

The DRAM Refresh circuitry is discussed in detail in section 2.3.11.

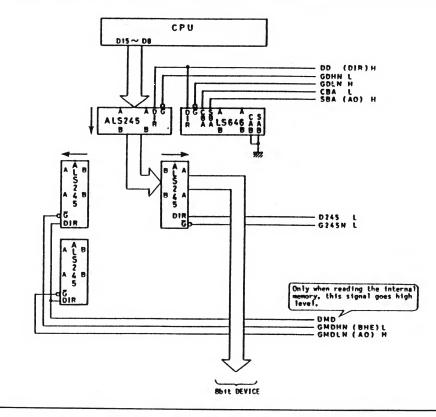

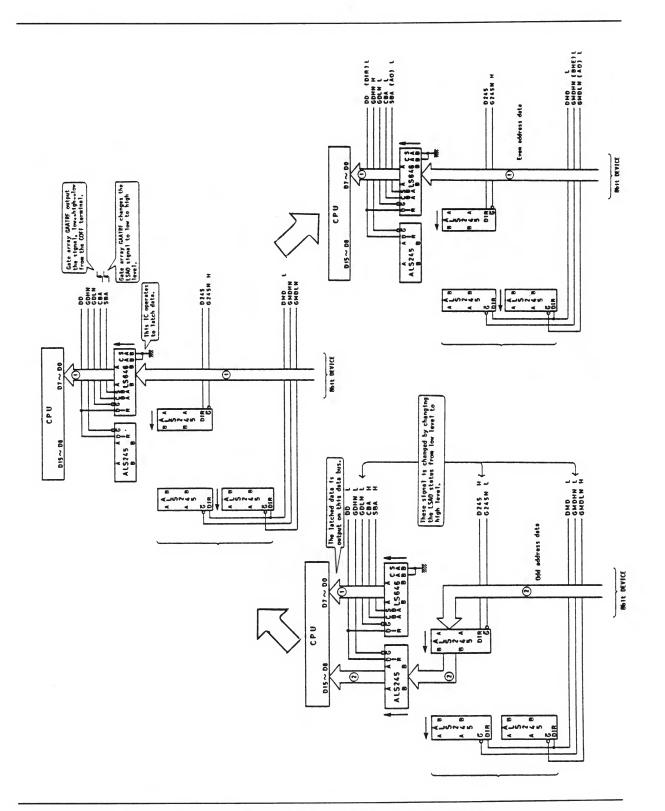

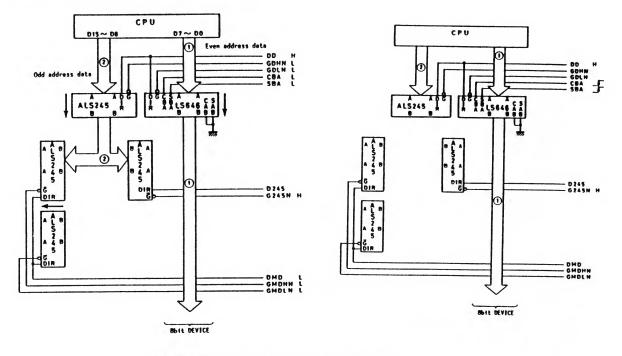

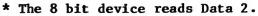

## 2.3.4 BYTE/WORD ACCESS & 16-8 BIT DATA CONVERSION

16-8 bit data conversion occurs during word transmission to an even address of an 8 bit device.

| MODE DA                                 | TA TRANSMISSION TO | REFERENCE            |

|-----------------------------------------|--------------------|----------------------|

| Byte transmission of EVEN address       | 16-bit device      | Figure 2-9           |

| Byte transmission of ODD address        | 16-bit device      | Figure 2 - 20        |

| Word transmission of EVEN address       | 16-bit device      | Figure 2-21          |

| Word transmission of ODD address        | 16-bit device      |                      |

| Byte transmission of EVEN address       | 8-bit device       | Figure 2-22          |

| Byte transmission of ODD address (read) | ) 8-bit device     | Figure 2 - 23/2 - 24 |

| Byte transmission of ODD address(write) | 8-bit device       | Figure 2-25          |

| Word transmission of EVEN address       | 8-bit device       | Figure 2 – 26        |

## TABLE 2-9. CPU DATA ACCESS MODE DIAGRAM LIST

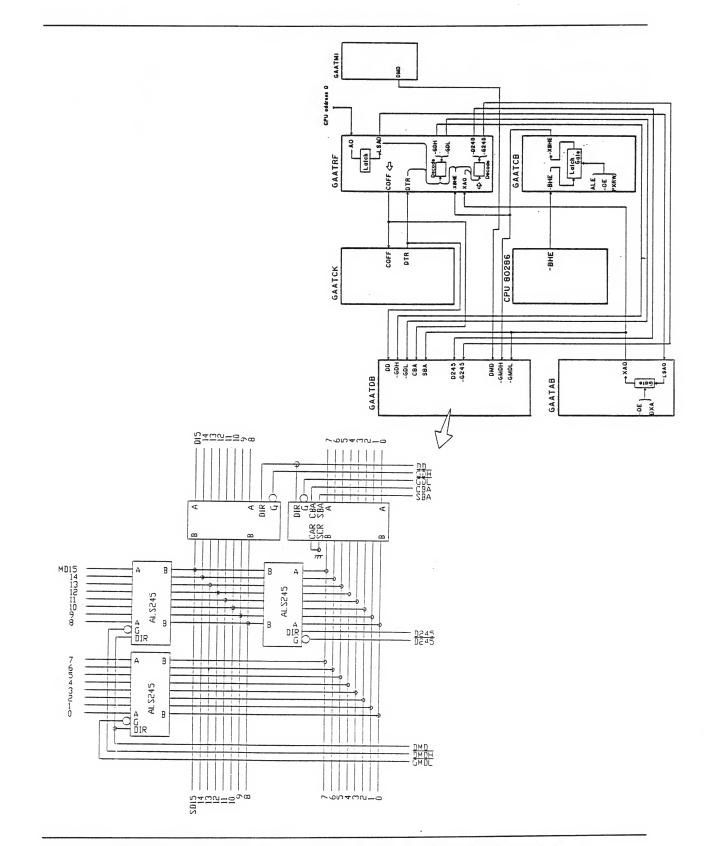

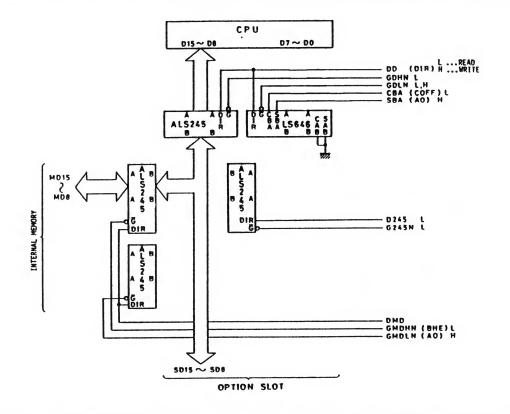

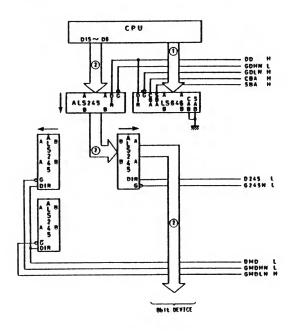

## 2.3.4.1 DATA BUS CONTROL SIGNAL ON GAATDB

The gate array GAATDB includes five 8 – bit buffers. These buffers use gate control and direction signals generated by other gate arrays. The following table describes gate control signals and direction signals.

| TABLE 2 – 10. FUNCTIONS OF CONTROL SIGN | NAL ON GAATDB. |

|-----------------------------------------|----------------|

|-----------------------------------------|----------------|

| NAME                                                | DESCRIPTION                                                                                                                                                                     |

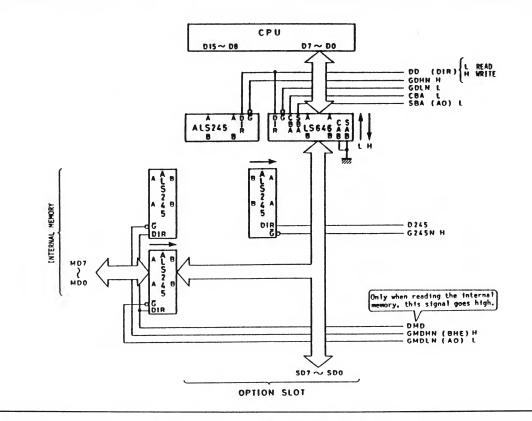

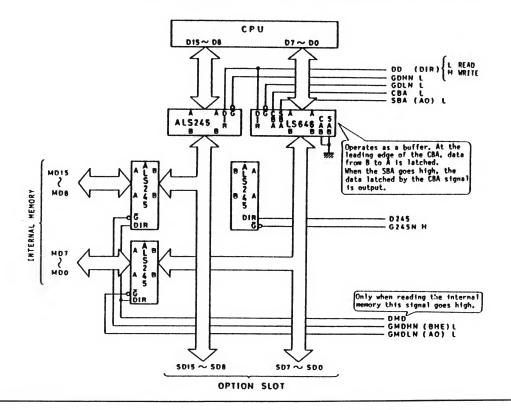

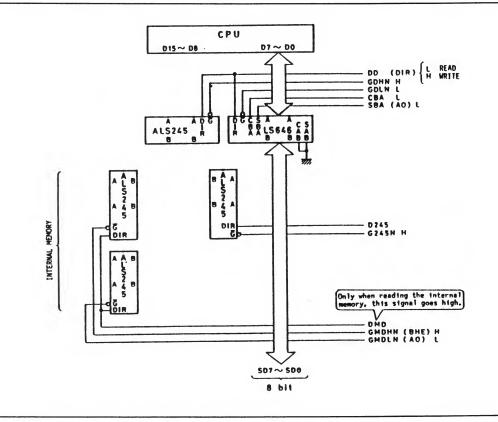

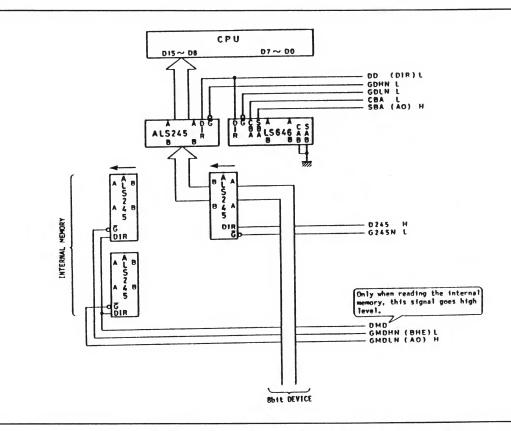

|-----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|